Читайте также:

|

Дана мікросхема використовується для організації обміну даними між оперативною пам'яттю і пристроями вводу/виводу по чотирьох незалежним каналам без участі МП. Такий обмін можна здійснювати блоками даних по 64 - 128 КБ, забезпечуючи перекриття адресного простору 16 МБ. В процесі обміну контролер прямого доступу до пам'яті (ПДП) обробляє всі необхідні керуючі сигнали і формує адреси комірок пам'яті, з якими здійснюється обмін. При цьому контролер ПДП виступає як ведучий пристрій, а виводи МП переводяться в третій стан.

УГЗ контролера ПДП типу 8237А представлено на рис. 2.18.

Рис. 2.18. УГЗ контролера ПДП

ИС має вісім інформаційних виходів D0 –D7, виходи восьми молодших розрядів адреси А0 – А7 (з них молодші чотири розряди – двонаправлені виходи), виходи запита прямого доступу DRQ і виходи дозволу прямого доступу.

Виходи керуючих сигналів:

RST – скидання;

- вибір кристала;

- вибір кристала;

С – синхронізація;

RDY – готовність;

HLDA – підтвердження захоплення;

HOLD – сигнал захоплення;

ADS – строб адреси;

EN – дозвіл адреси;

і

і  – запис і читання вводу/виводу;

– запис і читання вводу/виводу;

і

і  - запис і читання пам’яті;

- запис і читання пам’яті;

- закінчення процесу обміну.

- закінчення процесу обміну.

Внутрішня структура контролера ПДП типу 8237А представлена на рис.2.19.

Рис. 2.19. Внутрішня структура контролера ПДП

де БА, БД – буфери адреси, даних.

СУВВ – схема управління вводу/виводу,

K3 – K0 - канали ПДП,

БПУ – блок пріоритетів і управління.

Контролер містить: два буфера: 8-ми розрядний буфер даних БД, що зв’язує СШД з внутрішньою 8-ми розрядною шиною контролера; буфер адреси БА, зв’язаний з вісьмома молодшими розрядами системної шини адрес; схему управління вводу/виводу СУВВ; блок пріоритетів і управління БПУ; чотири канали прямого доступу K0 – K3. Кожен канал має два 16-ти розрядних регістра адреси (регістр базової адреси PrБА і регістр поточної адреса PrПА (PrТА)). Регістр PrБА – зберігає початкові значення адреси пам’яті. Цей регістр завантажується побайтно в МП разом з регістром PrТА в режимі програмування. Вміст PrТА в процесі виконання передач автоматично зменшується чи збільшується, а першого регістра не зменшується. При автоініціалізації вміст першого регістра використовується для відновлення початкового значення PrТА. Підрахувати вміст PrБА не можна. Кожен канал містить також два 16-ти розрядних регістра – лічильники циклів слів: базовий СтБ і поточний СтП (СтТ ). В процесі реалізації значення лічильника СтТ зменшується щоразу на одиницю, вміст СтБ лишається незмінним.

Кожен канал має 6-ти розрядний регістр режиму. Запис у відповідний регістр режиму здійснюється байтом, формат якого приведено на рис.2.20. Два молодших біта цього байта визнають канал, в якому буде записуватись інформація про його режим роботи.

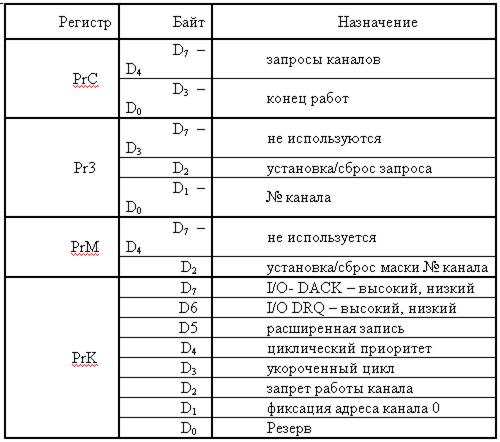

Кожен канал має також власні регістри запитів Pr3 и регістри маски PrМ (табл. 2.2.). Контролер ПДП може реагувати на запити прямого доступу, що ініціалізуються програмно подібно до надходження сигналу запиту прямого доступу DRQ. Розряди маски також можуть бути встановлені або скинуті програмно (є команди як роздільної, так і одночасної установки скидання розрядів маски).

У складі БПУ є два 8-ми розрядних регістра (регістр команд PrК і регістр стану PrС). Регістр PrК керує операціями, що виконує контролер і заповнюється при програмуванні контролера. Підрахувати інформацію з цього регістра МП не може.

Регістр PrС містить інформацію про стан каналів на даний момент часу і наявність запитів на обслуговування. Вміст цього регістра може бути прочитано МП. За допомогою керуючих сигналів  , а також чотирьох молодших розрядів адреси А3 – А0 можна записувати або зчитувати інформацію з усіх вище перелічених регістрів схеми 8237А. Обмін з регістрами контролера виконується тільки побайтно. Для завантаження 16-ти бітних значень використовується спеціальний тригер парності байт, розміщений в БПУ. При скиданні контролера по сигналу RST цей тригер встановлюється в нульовий стан, завдяки чому контролер буде підготовлений до прийому молодшого байта. Після прийому цього байта тригер змінює свій стан, завдяки чому контролер буде підготовлений до прийому старшого байта і т.д.

, а також чотирьох молодших розрядів адреси А3 – А0 можна записувати або зчитувати інформацію з усіх вище перелічених регістрів схеми 8237А. Обмін з регістрами контролера виконується тільки побайтно. Для завантаження 16-ти бітних значень використовується спеціальний тригер парності байт, розміщений в БПУ. При скиданні контролера по сигналу RST цей тригер встановлюється в нульовий стан, завдяки чому контролер буде підготовлений до прийому молодшого байта. Після прийому цього байта тригер змінює свій стан, завдяки чому контролер буде підготовлений до прийому старшого байта і т.д.

В контролері ПДП є спеціальні команди, які можуть бути виконані при програмуванні даної схеми:

- скидання тригера парності байт;

- програмне скидання;

- скидання регістра маски.

Контролер 8237А може працювати, використовуючи два типи пріоритетів, які встановлюються програмно. Перший – фіксовані пріоритети, коли пріоритет каналу відповідає зменшенню їх номерів; другий - циклічний, коли останній канал, що обслуговується, стає каналом з найнижчим пріоритетом (и далі по циклу). Такий режим дозволяє забезпечувати рівний доступ для всіх пристроїв вводу/виводу, що працюють за схемою 8237А.

Рис 2.20. Формат керуючого слова

Програмування контролера ПДП здійснює МП за допомогою команд вводу/виводу. Початкова ініціалізація контролера виконується одразу ж після увімкнення живлення. Адреса внутрішніх регістрів контролера визначаються кодом на виходах А3 – А0 . Для завантаження початкових значень кодів регістрів адрес каналів і лічильників циклів обміну, потрібно виконати по дві операції виводу.

Контролер ПДП може бути запрограмований для виконання наступних чотирьох режимів робіт:

одиночної передачі;

блочної передачі;

передачі за запитом;

передачі пам’ять – пам’ять.

Таблиця 2.2.

В комп’ютерах, починаючи з PС AT, використовується підсистема прямого доступу до пам’яті, що складається з двох контролерів. Другий контролер підключений до шини адреси зі зміщенням на один байт, тому він керує лініями адреси А[16-1], організовуючи обмін послівно. Для забезпечення доступності адресного простору пам’яті розміром 16 МБайт використовуються зовнішні 8-ми розрядні регістри сторінок PrCT.

Мікросхема 8237А каскадується шляхом підключення першого контролера до четвертого каналу другого контролера (рис. 2.21.).

Рис. 2.21. Система ПДП

Передача байт (DMA-1-контролер)

| 23 PrCt 16 | 15 PrCA 8 | 7 Ai 0 |

Передача слів (DMA-2-контролер)

| 23 PrCt 15 | 16 PrCA 9 | 8 Ai 1 |

Канали 0-3 забезпечують побайтову передачу блоками до 64 КБ, канали 5-7 забезпечують передачу 16-ти розрядних слів блоками до 128 КБ (64 КС), при цьому слова обов’язково повинні бути розміщені з дотриманням парних границь, тобто записуватись за парною адресою (А0 =0). Всі запити прямого доступу каналів 0-3 обробляються через 4-й канал другого контролера.

Рис.2.6.5. показує, як формується 24-розрядна адреса, що забезпечує перекриття адресного простору 16 МБ. При цьому молодший байт адреси зчитується з шин адреси А0 - А7 контролера 8237, другий байт зчитується з виходів D0 - D7 і запам'ятовуються в додатковому регістрі старшої адреси PrCA, вісім останніх розрядів адреси зчитуються з регістра сторінок PrCT, інформація в якій потрапляє із спеціальних комірок ОП.

Після програмування режимів роботи схеми 8237А, вона може забезпечити або передачу інформації з пристроїв вводу/виводу, при цьому виробляється наступна пара керуючих сигналів  або в зворотному напрямку, при цьому буде вироблятися пара сигналів

або в зворотному напрямку, при цьому буде вироблятися пара сигналів

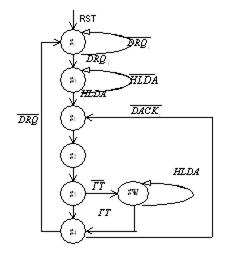

У блоці управління контролера ПДП є керуючий автомат, який може знаходитися в одному з 7 станів. При надходженні сигналу системного скидання RST контролер переходить в початковий стан. При цьому всі внутрішні регістри даної схеми обнуляються і ніяких дій по обміну інформацією не відбувається. Потім потрібна ініціалізація схеми ПДП. Після ініціалізації він буде продовжувати перебувати в початковому стані, поки будь-який з пристроїв I / О не сформує (рис. 2.22.).

У блоці управління контролера ПДП є керуючий автомат, який може знаходитися в одному з 7 станів. При надходженні сигналу системного скидання RST контролер переходить в початковий стан. При цьому всі внутрішні регістри даної схеми обнуляються і ніяких дій по обміну інформацією не відбувається. Потім потрібна ініціалізація схеми ПДП. Після ініціалізації він буде продовжувати перебувати в початковому стані, поки будь-який з пристроїв I / О не сформує (рис. 2.22.).

Рис. 2.22. Схема зміни станів ПДП

Як тільки контролер отримує такий сигнал, він одразу ж переходить в стан S0, при цьому виробляється сигнал захоплення, що надходить в МП. Отримавши сигнал ЗХ, МП переводить свої шини в третій стан і передає в контролер сигнал ПЗХ. Наявність такого сигналу переведе контролер в стан S1, пов’язаний з виробленням сигналу  , що передається в пристрій I/O. Стан S1 - початковий стан циклу передачі 1 байта інформації. Цей цикл включає стани S1 ,S2 ,S3 ,S4 .

, що передається в пристрій I/O. Стан S1 - початковий стан циклу передачі 1 байта інформації. Цей цикл включає стани S1 ,S2 ,S3 ,S4 .

Під час стану S2 контролер через СШД видає старший байт адреси комірки пам’яті, з якою буде здійснюватись обмін. Цей байт необхідно запам’ятати в деякому буферному проміжному регістрі. Старший байт адреси супроводжується сигналом АДS.

В стані S2 видається молодший байт адреси через виходи А0 –А7 . Порядок вироблення сигналів читання і запису визначається напрямком передачі, вони виробляються в циклах S2 ,S3 . Зі стану S3 в стан S4 можливий перехід через стан очікування (Sw), що залежить від наявності сигналу готовності.

Кількість циклів обміну визначається інформацією, що зберігається у відповідному лічильнику. При обнуленні лічильника операція обміну завершується, контролер переходить в початковий стан. В цьому стані він буде знаходитись до тих пір, поки не прийде черговий сигнал запиту прямого доступу DRQ.

Дата добавления: 2015-10-28; просмотров: 215 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Програмований контролер переривання 8259А | | | Інтервальний таймера 8254. |