|

Читайте также: |

286 МП є другим поколінням 16-розрядних МП. У порівнянні з МП8086, у цього МП збільшена розрядність шини адреси на 4, завдяки чому область ОП, що фізично адресується збільшилася до 4 МБ. Цей МП розроблявся для використання в багатокористувацьких системах, в ньому можна використовувати режим захищеної віртуальної пам'яті (30 дб. розрядів, 1 Гб).

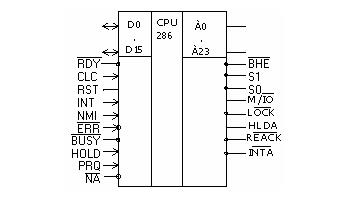

На рис. 1.14. представлено УГЗ 286 МП.

Рис. 1.14. УГЗ 286 МП

Де:

D0-D15 - шина даних

А0-А23 - шина адреси

BHE - передача байта

PRQ - запит співпроцесора

BUSY - «зайнято»

ERROR - «помилка» співпроцесора

PEACK - підтвердження ЗСП

LOCK - блокування.

Інші позначення були визначені раніше.

Структурна схема 286 МП представлена на рис.1.15.

Рис. 1.15. Структурна схема МП 80286

Де:

ПСШ - пристрій сполучення шини;

РЗП – регістри загального призначення;

АЛП – арифметично-логічний пристрій;

F – регістр ознак РГС;

MSW – регістр стану;

входять до складу РЗП ті ж регістри, що і в 86 МП;

В даному МП здійснюється конвеєрне виконання команд (одночасно - до 4 команд). Для реалізації такого режиму використовуються наступні блоки:

пристрій попередньої вибірки команд (ППВК);

чергу команд (ЧК), довжиною 6Б. Витягнуті з черги команди надходять на дешифратор команд, який перетворює кожну команду в 69-розрядну мікрокоманду, яка потрапляє в чергу мікрокоманд (ЧМК), що містить 3 мікрокоманди. Блок управління процесором містить керуючу пам'ять довжиною 1536 слів по 35 біт.

В даному МП є також блок перетворення адрес (БПА), який містить блок сегментних регістрів (як і в 86), блок суматора адреси (БСА) і кеш-пам'ять сегментних дескрипторів (КСД). Ця пам'ять складається з чотирьох 48-розрядних регістрів, кожен з яких має три поля: поле доступу (1 байт); поле бази (3 байта); поле обмеження (2 байти).

БПА в режимі реальної адресації RM працює подібно 86-му МП, формуючи при цьому 24-розрядний фізичну адресу шляхом складання ефективної адреси ЕА з вмістом одного з сегментних регістрів.

Програмістська модель містить 19 регістрів, довжина кожного з них дорівнює 16 біт. (рис.1.16.)

| AX | AH | AL |

| DX | DH | DL |

| CX | CH | CL |

| BX | BH | BL |

| BP | Покажчик бази | |

| SP | Покажчик стека | |

| SI | Індекс джерела | |

| DI | Індекс приймача | |

| IP | Указатель команд | |

| F | Регістр ознак | |

| MSW | ||

| Сегментні регістри | ||

| CS | команд | |

| DS | даних | |

| SS | стека | |

| ES | дод. даних | |

| TR | Регістр задачі | |

| LDTR | ||

| GDTR | ||

| IDTR |

Рис. 1.16.

- РЗП (AX,..., SI, DI) - вісім шістнадцятирозрядних регістрів;

- сегментні регістри (CS, DS, ES, SS) - чотири регістра;

- регістри управління та стану (F, IP, MSW);

Системні регістри включають TR - регістр задачі; LDTR - регістр селектора-сегмента таблиці локальних дескрипторів; GDTR - регістр селектора сегмента таблиці глобальних дескрипторів; IDTR - регістр адреси таблиці дескрипторів переривань.

В 286-му МП здійснюється робота в двох режимах:

- режимі реальної адресації пам'яті (RM);

- режимі захищеної віртуальної адресації (PM).

Перший режим подібний роботі режиму пам'яті 86-го МП: в цьому режимі формується виконавча адреса (20 розрядів) шляхом додавання вмісту одного з сегментних регістрів і 16-розрядного зміщення (ефективної адреси). Це однокористувацький режим. В реальному режимі доступна область фізичної пам'яті дорівнює 1МБ.

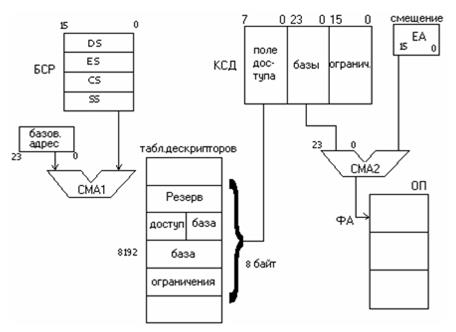

Другий режим - режим віртуальної захищеної адресації пам'яті, розмір якої 1 Гб. Реалізація відображення віртуального адресного простору на реальний адресний простір представлена на рис. 1.17.

Рис. 1.17.

Де:

БСР - блок сегментних регістрів;

СМА1, 2 - суматори адреси;

КСД - кеш-пам'ять сегментних дескрипторів (складається з 4 комірок, кожна довжиною по 48 байт). Ця пам'ять містить 3 поля: доступу (1 байт); бази (3 байта); обмеження (2 байти).

Для задання віртуального режиму використовується 32-х розрядний покажчик - віртуальна адреса, що складається з 16-розрядного зсуву в сегменті і селектора сегмента (16 розрядів).

Селектор сегмента, подібно базі сегмента 86-го МП, міститься в одному з чотирьох сегментних регістрів, визначає базову адресу, до якої для одержання фізичної адреси додається зсув.

Селектор сегмента містить 3 поля:

- RPL (2 біта) - рівень привілейованості сегмента;

- T (1 біт) - покажчик таблиці дескрипторів;

- зміщення (13 біт).

Весь віртуальний простір, розмір якого 1 Гб, розбивається на 2 області по 512 Мб, одна з них називається глобальною (GTR), інша - локальною (LTR). GTR доступна будь-яким завданням; LTR належить конкретному завданню користувача.

Будь-який сегмент, який необхідний для виконання завдання, задається за допомогою 64-розрядного описувача сегмента, який називається дескриптором.

Кожен дескриптор займає 8 послідовних адрес пам'яті і включає наступні поля:

- резервне (що містить нулі, 2 Б);

- доступу (1Б);

- бази (3Б);

- обмеження (2Б) - визначає розмір сегмента (цей розмір може бути від 1 байта до 215Б).

Загальна кількість дескрипторів таблиці, яка зберігається в загальній оперативної пам'яті, дорівнює 8192. Число таблиць - 2. Біт Т в полі доступу визначає відповідну таблицю:

- для глобальної області (Т = 0);

- для локальної (Т = 1).

Для вибору одного з 8192 дескрипторів використовуються 13 розрядів.

Базові адреси відповідних таблиць зберігаються в одному з відповідних регістрів МП.

Сегменти бувають різних типів. Тип відповідного дескриптора сегмента визначається розрядом S в полі доступу.

Якщо S = 1 - сегмент команд або даних.

S = 0 - системний сегмент.

Інші розряди поля доступу мають наступний зміст:

Біт Р - наявність (Р = 1) або відсутність (Р = 0) сегментів у пам'яті.

DPL - визначає пріоритет сегмента (існують 4 рівні пріоритету):

рівень 0 - присвоюється ядру операційної системи;

рівень 1, 2 – програмному розширенню ОС;

рівень 3 - призначений для користувача рівень.

Значення поля Тип залежить від типу сегмента. Наприклад, якщо S = 1, три розряду цього поля мають сенс: ознака можливості читання або записування; ознака підпорядкування; ознака виконуваності.

У групі системних сегментів з'являється поняття «шлюзу». Шлюз - певний вид сегмента (системного), який використовується при зверненні до інформації, що знаходиться на рівні привілейованості, що відрізняється від поточного.

Процес перетворення віртуальної адреси складається з етапів: звернення до відповідної таблиці дескрипторів, зчитування відповідного дескриптора і порівняння ліченої інформації з вмістом кеш-пам'яті. Якщо сегмент знаходиться в кеш-пам'яті і його можна виконати (аналіз рівня привілейованості дозволяє виконання), то поле бази зчитується з кеш-пам'яті і подається на другий суматор, на виході якого і формується фізична 24-х разрядна адреса, за якою здійснюється звернення до оперативної пам'яті.

Якщо ж інформація про якийсь сегмент в ОП відсутня (про що свідчить порівняння з кеш-пам'яттю), тоді відповідний сегмент перекачується із зовнішньої ОП.

Завдяки такому рішенню створюється ілюзія про наявність в ЕОМ віртуальної пам'яті розміром 1 Гб при її реальних розмірах 16 Мб.

Дата добавления: 2015-10-28; просмотров: 154 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Арифметичний співпроцесор 8087 | | | Мікропроцесор 80386 |