|

Читайте также: |

Мікропроцесорні системи

ЗМІСТ

ВСТУП

1. Однокристальні універсальні мікропроцесори

1.1. Класифікація мікропроцесорів (МП)

1.2. Восьмирозрядний мікропроцесор i8080

1.3. Восьмирозрядні мікропроцесори 8085 і Z80

1.4. Шістнадцятирозрядний мікропроцесор 8086

1.5. Арифметичний співпроцесор 8087

1.6. Мікропроцесор Intel 8088

1.7. 16-розрядний мікропроцесор 80286

1.8. Мікропроцесор 80386

1.9. Арифметичні співпроцесори 80287 і 80387

1.10. Мікропроцесор 486 DX

1.11. Мікропроцесор Pentium

1.12. Мікропроцесор Pentium Pro, Pentium II

1.13. Мікропроцесор AMD-K6

1.14. Оцінка продуктивності МП

2. Схеми підтримки. Контролери

Склад схем підтримки

Буферні регістри ТА шинні формувачі

Програмований паралельний інтерфейс 8255

2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

2.5. Програмований контролер переривання 8259А

2.6. Контролер прямого доступу до пам’яті 8237А

2.7. Інтервальний таймера 8254

2.8. Система реального часу

3. Процесори зі скороченою кількістю команд (RISC-процесори)

3.1.Особливості RISC-процесорів

3.2. RISC-процесор Alpha 21164 компанії DEC

3.3. RISC-процесор PowerPC620

3.4. RISC-процесор MIPS-10000

3.5. RISC-процесор РА-8000

3.6. RISC-процесор UltraSPARC ІІ

3.7. RISC-процесори UltraSPARC ІІІ, UltraSPARC ІV

4.Системні ресурси та системні шини. Чипсети

4.1. Системні шини

4.2. Розподіл і організація пам'яті ПК

4.3. Кеш пам’ять

4.4. Чипсети

4.4.1. Характеристика чипсетів

4.4.2. Чипсети серії 440

5. Цифрові сигнальні процесори (DSP)

5.1. Алгоритми обробки цифрової інформації та області застосування сигнальних процесорів

5.2. Особливості роботи сигнальних процесорів

5.3. DSP сімейства TMS320С1Х

5.4. Сигнальні процесори сімейства TMS320С2Х.

5.5. Процесори DSP сімейства TMS 320C5X

5.6. Сигнальні процесори TMS320C2XX І 320С54Х

5.7. Сигнальний процесор TMS320С30

5.8. Сигнальні процесори сімейства TMS320С4Х

5.9. Сигнальні процесори сімейства TMS320C8X

5.10. Процесор сімейства TMS320C62XХ

5.11. DSP процесори сімейства TMS320C67Х

5.12. Сигнальні процесори DSP сімейства ADSP21XX

5.13. Сигнальні процесори DSP сімейства АDSP 21ХХХ

6. Мультипроцесорні обчислювальні системи

6.1. Класифікація обчислюваних систем

6.2. Характеристика СуперЕОМ серії Cray

6.3. Системи з масовим паралелізмом

6.4. Закон Амдала

6.5. Закон Густафсона

6.6. Грід – система

6.6.1. Ресурси Грід

6.6.2. Архітектура Грід-систем

6.6.3. Протоколи глобального Гріда

ВСТУП

Даний учбовий посібник «Мікропроцесорні системи» з навчальної дисципліни «Мікропроцесорні системи» складається з шести частин:

- Однокристальні універсальні мікропроцесори;

- Схеми підтримки. Контролери;

- Процесори зі скороченою кількістю команд (RISC-процесори);

- Системні ресурси та системні шини. Чипсети;

- Цифрові сигнальні процесори (DSP);

- Мультипроцесорні обчислювальні системи.

Він призначений для студентів спеціальності «Інформаційні уравляючі системи та технології» напряму «Комп'ютерні науки».

1. ОДНОКРИСТАЛЬНІ УНІВЕРСАЛЬНІ МІКРОПРОЦЕСОРИ

1.1. Класифікація мікропроцесорів (МП)

Найважливішою складовою частиною будь-якого персонального комп'ютера (ПК) є його центральний процесор. Розвиток інтегральної технології привів до появи великих і надвеликих інтегральних схем (ВІС і НВІС), що містять на одному кристалі (в одному корпусі - чіпі) десятки, сотні тисяч, а в останніх виробах і кілька мільйонів елементарних транзисторів. На базі таких схем і були створені мікропроцесори (МП), в яких на одному чіпі реалізовані функції центрального процесора комп'ютера і тому вони називаються однокристальними. Перший однокристальний чотирирозрядний МП i4004 був розроблений компанією Інтел (Intel) в 1971 році, яка до теперішнього часу є безумовним лідером в проектуванні сучасних МП. Незабаром компанія Інтел випускає восьмирозрядний мікропроцесор i8008 і його вдосконалений варіант i8080. Класична архітектура останнього МП справила величезний вплив на розвиток однокристальних МП, проте для свого першого персонального комп'ютера IBM PC компанія IBM вибрала інший мікропроцесор i8088, випущений компанією Intel в 1977 році, який належить до першого покоління 16-розрядних МП і є модифікацією процесора i8086, який з'явився роком раніше. Обидва процесора підтримували область пам'яті в 1 Мбайт і мали відповідно 8 і 16-розрядну шину даних. З програмної точки зору ці МП ідентичні, їхня система команд і набір процесорних регістрів включена в усі вироби PC сумісних комп'ютерів; їх по праву називають родоначальниками сімейства х86 мікропроцесорів.

МП типу 80286 представляє друге покоління 16-розрядних МП, був випущений в 1982 році. Найсуттєвішою відмінністю від МП типу 8086 була наявність механізму управління адресацією пам'яті, підтримка віртуальної пам'яті, забезпечення чотирирівневої системи захисту. Використання виконавчої адреси розрядністю 24 біта дозволяло адресувати 16 Мбайт фізичної пам'яті. Спеціальні засоби МП підтримували механізм перемикання завдань (Task switching). 286 МП використовує розширену систему команд, включаючи всі команди 8086 МП.

Історія 32-розрядних МП почалася з процесора Intel 386, який був випущений в 1985 році. Друге покоління 32-розрядних МП представляв процесор Intel 486, в якому використовувалася внутрішня кеш-пам'ять і арифметичний співпроцесор.

Процесори Pentium - п'яте покоління сімейства 80х86, що складається з процесорів P5, P54, Pentium MMX. З моменту появи МП Pentium Pro прийнято відлічувати початок шостого покоління P6. Процесор Pentium II, який був випущений в 1997 р. представляє собою поєднання архітектури процесорів Pentium Pro з технологією MMX. Наведемо в таблиці 1.1 порівняльні характеристики процесорів Intel сімейства 80х86 і Pentium.

Таблиця 1.1 - Основні характеристики процесорів Intel.

| тип | 80386DX | 80386SX | 80486DX | 80486SX | 80486DX2 | P5 | Pro | P II | |||||

| рік | |||||||||||||

| число транзис-торів | 5 тыс | – | 134 тыс | 275 тыс | 275 тыс | 1,2 млн | 1,18 | 1,38 млн | 3,1 | 5,5/15,5/31 млн | – | ||

| число виходів | |||||||||||||

| F | 5,8, 10 | 5,8, 10 | 5, 10 | 8, 12, 20, 25 | 16,20, 25,33, 40 | 16,20, 25, 33 | 20,25, 33,40, 50 | 16,20, 25, 33 | 50, 60 | 60,66, 100, 133 | 166, 180, 200 | 233/2,300 | |

| A/D | 16/8 | 20/16 | 20/8 | 20/16 | 24/16 | 32/32 | 24/16 | 32/32 | 32/32 | 32/32 | 32/64 | 64/64 | 64/64 |

| продук-тивність (млн. оп/сек.) | 0,03 | 0,33 | 0,33 | 0,6 | 1,2 | 4,5 | 16,5 | – |

Традиційними розробками універсальних однокристальних процесорів із «звичайним» набором команд, які називаються CISC-процесорами, є, крім Intel, компанії AMD і Cyrix, що випускають «інтелоподібні» процесори. Найбільшими розробниками універсальних комп'ютерів з скороченим набором команд, які називаються RISC-процесорами, вважаються Sun Microsystems (процесори UltraSparc), Digital Equipment (процесори Alpha) MIPS Technology (процесори Rxx00), Hewlett Packard (процесори PA-RISC x000), IBM і Motorola (процесори Power PC 6xx), які випустили кілька поколінь своїх виробів. На початку 80р в класі однокристальних приладів крім МП, з'явилися мікросхеми, що отримали назву мікроконтролерів. Фактично це ті ж однокристальні мікропроцесорні БІС, розширені схемами оперативної і постійної пам'яті, інтерфейсними схемами для підключення пристроїв вводу/виводу. Часто ці БІС називають все в одному (All in one).

Компанія Intel також випустила кілька поколінь мікроконтролерів: восьмирозрядних (8048, 8051), 16-розрядних (80188, 80186), 32-розрядних (80386EX).

Особливу групу складають процесори спеціального призначення, а саме, процесори для цифрової обробки сигналів, що називаються сигнальними процесорами (DSP). Провідна роль у випуску сигнальних процесорів належить компаніям Analog Devices (DSP типу 21хх і 210хх), Texas Instruments (DSP типу TMS320Cxx) і Motorola (56002,96002). Таким чином, в даний час можна виділити 3 напрямки розвитку МП-виробів інтегральної електроніки: однокристальні універсальні мікропроцесори з фіксованим числом розрядів (8, 16, 32, 64), зі звичайним набором команд - CISC, зі скороченим - RISC.

Однокристальні мікроконтролери, до складу яких включені, крім власне процесора, порти вводу/виводу, модулі оперативної і постійної пам'яті, схеми послідовного і паралельного інтерфейсів.

Процесори спеціального призначення називаються процесорами для цифрової обробки сигналів або сигнальними процесорами.

Восьмирозрядний мікропроцесор i8080

Даний восьмирозрядний мікропроцесор використовував n-МОН канальну технологію, вимагав для свого живлення три джерела напруги +5В, -5В, +12 В, працював на частоті 2 МГц, випускався в корпусі, що має 40 виходів.

Архітектурні особливості даного МП: 3-х шинна організація; що включає двонаправлену 8-розрядну ШД, 16-розрядну ША і шину управління (ШУ).

Навантажувальна здатність цих шин мала і дорівнює 1, тому підключення МП до системної шини повинно здійснюватися через спеціальні схеми шинних формувачів ШФ.

Використання 16-розрядної ША дозволяє адресувати 64Кб пам'яті і 256 зовнішніх пристроїв.

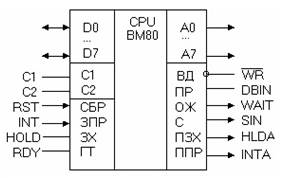

УГЗ мікропроцесора 8080 приведено на рисунку 1.1.

Рис. 1.1.

де D0 - D7 - шина даних, А0 - А7 - шина адресу.

ШУ включає:

два входи С1, С2, на які надходять дві зсунуті на півперіоду серії С1, С2, що тактують з максимальною частотою 2 МГц;

С - вих. сигнал тактування;

RST - скидання (установка мікропроцесора у вихідний початковий стан);

INT - вхідний сигнал запиту переривання;

INTA - підтвердження переривання;

RDY - сигнал готовності;

WAIT - сигнал очікування;

HOLD - сигнал захоплення;

HLDA - підтвердження захоплення;

DBIN - прийом;

- видача

- видача

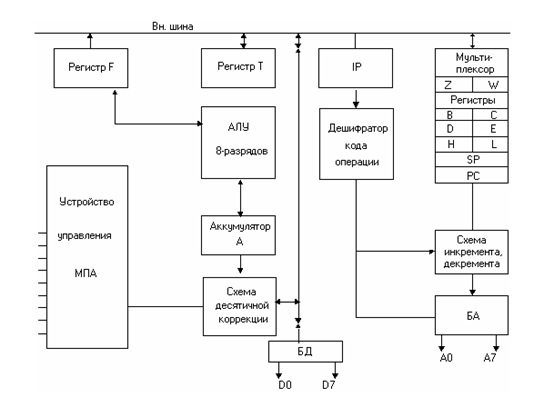

Структурна схема приведена на рис. 1.2.

Рис. 1.2.

Схема включає наступні блоки:

Блок регістрів мікропроцесора, що містить ряд програмно доступних регістрів:

- регістр акумулятора А (вісім розрядів);

- регістр F - регістр ознак результату (8 р.), що використовує наступні 5 ознак результату (рис.1.3.);

| S | Z | AD | Y | X | P | x | C |

Рис. 1.3. Схема регістру F

- сьомий розряд - ознака S - знак числа (0 - «+», 1 - «-»); Z - ознака результату рівного «0»; С - ознака переповнення - перенесення з восьмого (самого старшого) розряду; АС - половинний перенос (з молодшої тетради в старшу); Р - розряд паритету (парності);

- група внутрішніх регістрів мікропроцесора (РОНи): B, C, D, E, H, L.

Відповідну пару регістрів можна використовувати як один 16-розрядний (регістри H, L називаються регістрами непрямої адресації);

SP - покажчик вершини стека (16 р.); РС - лічильник команд (16 р.); Програмно-недоступні регістри - Z, W.

Операційний пристрій, що складається з восьмирозрядного АЛП; регістра тимчасового зберігання коду одного з операндів Т; схеми десяткової корекції; схеми інкремента (декремента), що дозволяє збільшити (зменшити) зміст лічильника команд PC.

Блок управління, що складається з восьмирозрядного регістра команд IP; дешифратора коду операції (DC); вузла вироблення керуючих сигналів.

Інтерфейсний блок включає буфер даних (БД), буфер адреси (БА).

Мікропроцесор 8080 містить внутрішню восьмирозрядний шину.

Система команд МП включає 78 базових інструкцій.

Команди мають довжину 1-3 байта, займають від 1 до 3 комірок оперативної пам'яті, потребують для виконання 1-5 маш. циклів (М1,..., М5), кожен з яких містить 3-5 маш. тактів (Т1,..., Т5). Тривалість машинного такту при тактовій частоті 2МГц дорівнює 500 нсек, в цьому випадку найкоротша команда виконується за 2 мсек. (містить 1 маш. цикл і 4 маш. такту). Найдовша - за 18 мсек.

Будь-яка команда обов'язково містить цикл М1 - вибірку команд. МП, використовує три типи форматів команд (рис. 1.4.). Однобайтний формат використовується для представлення команд з неявною, регістровою чи непрямою адресацією і дозволяє адресувати операнди, що містяться у регістрах МП та комірках ОП. Двобайтний формат використовується в командах з безпосереднім операндом чи з прямою адресою порту вводу/виводу (другий байт команди). У другому та третьому байтах трибайтних команд міститься 16-розрядна пряма адреса комірки пам'яті.

Багатобайтні команди зберігаються в сусідніх комірках пам'яті ЗП та адресуються за першим байтом.

Рис.1.4. Формат команд МП І8080

Якщо команда написана на Асемблері, вона являє собою послідовність операндів в кожному рядку і має 4 поля:

1-е - ім'я;

2-е - операція:

3-е - операнд:

4-е - примітка.

Розглянемо деякі оператори, які породжують машинну команду. При цьому використовується наступна символіка:

А - акумулятор;

В, С.... - регістри загального призначення;

ADDR - 16 розрядні адреси;

D8 - 8 розрядні дані;

D16 - 16 розрядні дані;

R1, R2,.. РОНи;

RP - пара регістрів;

RPH - старший регістр пари;

RPL - молодший регістр;

SP - вершина стека;

F - регістр ознаки;

М - комірка пам'яті

Таблиця 1.2 - Таблиця адресації регістрів:

| ddd sss | rp | ||

| B C D E H L M A | BC DE HL SP | ||

Команди пересилки даних.

2. Команди арифметичних операцій.

3. Команди логічних операцій.

4. Команди передачі керування.

5. Команди вводу/виводу, роботи зі стеком і спеціальні.

В машинному такті Т1 циклу М1 вміст програмного лічильника PC видається на шину адреси і надходить в ОП. В цей же час з'являється вих. сигнал синхронізації С і на шині даних з'являється байт стану БС мікропроцесора МП. Значення цього байта визначається типом машинного циклу (таких типів існує 9). БС потрібно запам'ятати в додатковому регістрі мікропроцесора, так як цей байт на ШД існує дуже короткий час (див. таблиця БС).

У такті Т2 перевіряється наявність сигналів готовності та захоплення. Якщо сигнал RDY присутній, то з Т2 можна перейти в Т3, інакше перехід можливий тільки через стан очікування. В такті Т3 інформація з ШД надходить в регістр команд IP мікропроцесора. Прийнята інструкція дешифрується дешифратором коду операції. Якщо команда має довжину 1 байт, то можливе виконання тактів Т4, Т5, які будуть останніми.

Якщо виконуються більш довгі команди, то після Т5 будуть виконані наступні цикли. В таких командах інформація буде запам'ятовуватися в регістрах тимчасового зберігання Z і W.

Якщо в будь-якому з тактів Т1, Т2, Т3 виробляється сигнал INT, він може бути обслужений мікропроцесором тільки після повного завершення виконання поточної команди.

Таблиця 1.3 - Таблиця байту стану МП

| Позначення | Вив | ЗП | ЧП | ВС | ЗС | |||

| D0 | ОПР | INTA | обслуговув. прерив. | |||||

| D1 |

|

| запис-вихід | |||||

| D2 | СТК | STACK | стек | |||||

| D3 | ЗУП | HLDA | зупинка | |||||

| D4 | ВЫВ | OUT | вихід | |||||

| D5 | М1 | M1 | ознака маш. циклу вив. | |||||

| D6 | ВВ | IN | введення | |||||

| D7 | ЧТП | MEMR | читання пам'яті |

Як сказано вище, існують 9 різних машинних циклів: вибірка команди; читання з пам'яті; запис в пам'ять; запис у стек (ЗС); читання стека; введення з зовнішнього пристрою інформації в мікропроцесор; вивід у зовнішній пристрій; обробка переривань; зупинка.

Тип машинного циклу залежить від виконуваної команди, проте будь-яка команда починається з циклу «вибірка». Операція «читання» відрізняється від вибірки тільки тим, що інформація, яка надходить на шину даних з ОП записується не в регістр команд, а в один з РОНів МП. У складних мікропроцесорних системах вже недостатньо тих вихідних керуючих сигналів, які виробляються на шинах МП. У таких системах необхідно виробляти додаткові керуючі сигнали (вони виробляються з байта станів). Як правило, вироблення керуючих сигналів здійснюється в пристрої, званому системним контролером. Окремі розряди байта станів мають наступний зміст: сигнал D0 визначає момент початку реакції МП на переривання, він використовується для синхронної передачі вектора переривання із зовнішнього пристрою, який сформувало сигнал запиту переривання в МП; сигнал D1 говорить про те, що в даному машинному циклі буде здійснюватися запис інформації в пам'ять або виведення інформації у зовнішній пристрій; сигнал D2 є ознакою того, що в даному машинному циклі буде виконано звернення до ділянки пам'яті, обраному в якості стека; при цьому на шині адреси МП буде присутня адреса вершини стека; сигнал D3 визначає стан МП, викликаний командою «зупинка»; сигнал D4 є ознакою того, що в даному машинному циклі буде здійснюватися видача інформації у зовнішній порт. При цьому на шині адреси МП буде присутня адреса цього порту, а в момент появи сигналу «видача» на шині даних з'являється байт виведеної інформації; сигнал D5 - ознака машинного циклу М1-вибірки; сигнал D6 - введення - ознака того, що в даному машинному циклі буде здійснено введення інформації із зовнішнього порту; при цьому на шині адреси присутня адреса цього порту, а на шині даних - байт даних, що вводяться; цей байт фіксується в МП в момент появи сигналу прийому; сигнал D7 - читання пам'яті.

Дата добавления: 2015-10-28; просмотров: 432 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| St Peronne October 1916 | | | Восьмирозрядні мікропроцесори 8085 і Z80 |