|

Читайте также: |

Даний МП є процесором п'ятого покоління, має 64-розрядну шину даних і 32-розрядну шину адреси. Містить на чипі 3,1 млн. транзисторів. Відмінні риси МП Pentium;

Використовує суперскалярну архітектуру.

Має роздільну кеш-пам'ять першого рівня: для даних - 8 КБ, для команд - 8 КБ.

Вперше в цьому МП реалізована конвеєрна обробка операндів з плаваючою комою.

Даний МП має спеціальний блок динамічного передбачення розгалуження.

Містить 2 п'ятистадійних блока виконання інструкцій, які за 1 машинний такт можуть обробляти дві інструкції.

Організовано контроль адреси по парності.

Містить вбудований контролер переривань.

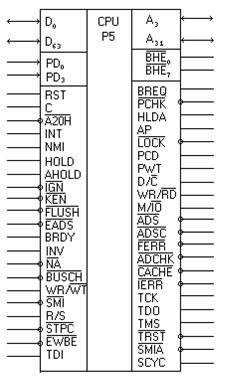

Умовне графічне зображення МП показано на рис. 1.24.

Рис.1.24. УГЗ МП Pentium

Де:

PD – паритет даних

- строб даних

- строб даних

- маска 20-го разряду адреси

- маска 20-го разряду адреси

AHOLD – захоплення адреси

- ігнорування помилки співпроцесора

- ігнорування помилки співпроцесора

- розширення пам’яті для кешування

- розширення пам’яті для кешування

- доступ до кеш-пам’яті

- доступ до кеш-пам’яті

- повне очищення кеш-пам’яті

- повне очищення кеш-пам’яті

- дійсна адреса співпроцесора

- дійсна адреса співпроцесора

INV – недійсний рядок кеш-пам’яті

- наступна адреса

- наступна адреса

- контроль шини

- контроль шини

- запис зворотній/наскрізний в кеш-пам’яті

- запис зворотній/наскрізний в кеш-пам’яті

- управління системою переривань

- управління системою переривань

- робота/стоп

- робота/стоп

- припинення внутрішньої синхронізації

- припинення внутрішньої синхронізації

- зовнішній буфер пустий

- зовнішній буфер пустий

TDI – вхід тесту даних

TDO – вихід тесту даних

TMS – вибір типу тесту

ТСК – синхронізація тесту

- закінчення тестування

- закінчення тестування

- помилка паритету даних

- помилка паритету даних

АР – біт паритету даних

- контроль паритету адреси

- контроль паритету адреси

- виявлення внутрішньої помилки

- виявлення внутрішньої помилки

- активізація системи управління перериваннями

- активізація системи управління перериваннями

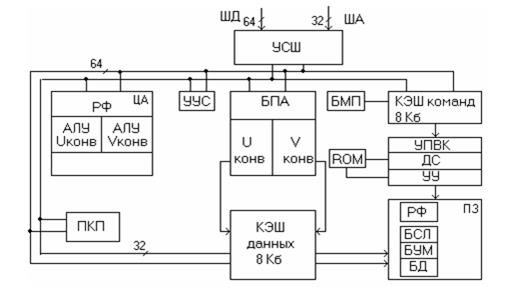

Примітка: деякі сигнали, які були введені при розгляді 486МП тут додатково не згадуються, деякі сигнали в УГЗ не наведено, наприклад сигнал управління множенням частоти, управління роботою МПС у 2-х процесорному варіанті. Структурна схема МП Pentium представлена на рис 1.25. і включає:

Рис. 1.25. структурна схема МП Pentium

ПСШ - пристрій сполучення з системною шиною, два внутрішніх роздільних кеша по 8Кб для даних і команд, конвеєрно виконавчий пристрій цілочисельної арифметики, що складається з двох конвеєрних модулів U і V, регістр зсуву і реєстровий файл (РФ); операційний пристрій обробки операндів СПЗ, що містить регістровий файл, конвеєрні блоки множення БМН, складання БСК і ділення БД. Управління процесом виконання команд реалізує УПВК - пристрій попередньої вибірки команд (два буфера по 3 2Б), дешифратор DC, керуюча пам'ять ROM.

Блок перетворення адреси (БПА) також включає в себе два конвеєра U і V. На кристалі МП розташовується вбудований контролер переривань ПКП, ПУС - пристрій управління сторінками. В даному МП вперше реалізований метод передбачення розгалужень (точки переходів запам'ятовуються в буфері міток переходів БМП). Подібно МП 486 використовується п'ятистадійне конвеєрне виконання інструкцій, що включає: попередню вибірку команд (1), декодування команд (2), генерацію (обчислення) адреси (3), виконання (4), запис результату (5). На рис 1.26. зображена послідовність проходження команд через конвеєр МП 486.

| K1 | К2 | К3 | К4 | К5 | |||||

| Kl | К2 | К3 | К4 | К5 | |||||

| K1 | К2 | К3 | К4 | К5 | |||||

| K1 | К2 | К3 | К4 | К5 | |||||

| K1 | К2 | К3 | К4 | К5 |

Рис 1.26.

Відмінність даного мікропроцесора від 486 полягає в тому, що в МП Pentium таких конвеєрів два, що дозволяє за один такт реалізувати не одну, а дві команди. Іншими словами, наявність двох буферів в ППВК дозволяє на кожній стадії обробляти паралельно по дві інструкції, які будуть надходити з конвеєра U і V. Рис. 1.27. ілюструє процес проходження інструкцій в МП Pentium.

| K1 | К3 | К5 | К7 | К9 | ||

| К2 | К4 | Кб | K8 | К10 | ||

| K1 | К3 | K5 | К7 | К9 | ||

| К2 | К4 | К6 | K8 | К10 | ||

Рис. 1.27.

Конвеєр U може виконати будь-яку інструкцію; V - конвеєр - тільки так звані прості команди, які визначаються спеціальними правилами спарювання команд. При паруванні V - конвеєр завжди виконує команду, наступну за командами U - конвеєра. Для того, щоб дві команди можна було виконати паралельно встановлені спеціальні правила спарювання, які вимагають, щоб обидві команди були «простими», між командами не повинно бути реєстрових залежностей типу «запис після читання» або «читання після запису», жодна з команд не повинна одночасно містити зсув або безпосередній операнд. «Простими» вважаються такі типи цілочисельних команд: команди пересилання, арифметичні і логічні команди, операції над стеками, завантаження, команди передачі управління. «Прості» команди виконуються, як правило, за один машинний такт. Як згадувалося, реалізація команд здійснюється за допомогою 5-ти ступеневого конвеєра. Перший ступінь - попередня вибірка команд реалізується за допомогою двох незалежних 32-розрядних буферів попередньої вибірки і переходів. У кожен момент часу працює тільки один з буферів. Попередня вибірка здійснюється послідовно до тих пір, поки не буде вибрана команда переходу. За результатами передбачення або триває послідовна вибірка, або включається інший буфер, який починає вибирати команди починаючи з тієї, на яку повинен бути виконаний перехід. Якщо перехід передбачений помилково, то конвеєр команд очищається і попередня вибірка починається знову. На другому щаблі два паралельно працюючих дешифратора команд дешифрують і відправляють на виконання дві послідовні команди, визначаючи, чи можна ці команди спаровувати чи ні. На третій стадії визначаються адреси операндів в пам'яті. На четвертій стадії виконується операція в конвеєрних АЛП і звернення до кеш-пам'яті даних. На цій стадії всі реалізовані в U і V - конвеєрах команди перевіряються на правильність передбачення переходів. На останній стадії здійснюється запис результату. Використання роздільних кеш-пам'яті команд і даних дозволяє ліквідувати конфлікти, що виникають при одночасному зверненні до команд і даних. У зв'язку з тим, що МП Pentiium створювався для використання в мультипроцесорних системах, необхідно передбачити спеціальні заходи, при роботі з кеш-пам'яттю декількох процесорів. Для цього був розроблений спеціальний механізм, названий кеш-узгодженням. Кеш-узгодження використовує спеціальний протокол MESI (modified, exclusive, shared, invalid). Згідно з цим протоколом, кожен рядок кеш-пам'яті повинен мати два біта статусу, що визначають один з чотирьох станів: стан М (змінений рядок). Рядок доступний тільки в одній кеш-пам'яті. Зміст його було змінено, тому такий рядок у загальній ОП відсутній. Стан Е (винятковий рядок). Рядок також доступний тільки в одній кеш-пам'яті, проте він не змінювався, тому його копія є в ОП. Стан S (розділений рядок). Такий рядок присутній більше ніж в одному кеші. Стан I (недійсний рядок). Рядок недоступний в кеш пам'яті. Читання 1-рядка призводить до зчитування відповідної ділянки з ОП в кеш-пам'ять при оновленні даних в кеш-пам'яті можна використовувати або наскрізний запис, коли запис йде паралельно (як в МП 486), так і зворотний запис, коли інформація записується тільки в кеш пам'ять змінений рядок кеш пам'яті переписується в ОП тільки, якщо цей рядок з якої-небудь причини повинен бути вилучений з кеш-пам'яті. На додаток до базової структури внутрішніх регістрів 486 МП в процесорах Pentium є набір регістрів MSR (Model Specific Registers - специфічних для моделі). У їх число входить група тестових регістрів (TR1... TR12), засоби моніторингу продуктивності, регістри фіксатори адреси і даних циклу. Тестові регістри дозволяють управляти більшістю функціональних блоків процесорного ядра, забезпечуючи можливість визначення їх працездатності. Засоби моніторингу продуктивності включають 64-розрядний таймер реального часу і лічильники подій. Лічильники подій CRO і CR1 розрядністю 40 біт, програмуються на підрахунок подій різних класів, пов'язаних з виконанням команд, шинними операціями, подіями у внутрішніх вузлах конвеєрів, кеш, контролем точок зупинки і т.п. Поле типу подія довжиною 6 біт дозволяє кожному лічильнику незалежно визначати, які події з великого списку він буде відстежувати. Стан лічильників може задаватися, і зчитуватися програмно. Для процесорів Pentium джерелами апаратних переривань є такі їх вхідні сигнали, які перераховані в порядку убування їх пріоритетів:  - контроль шини, R /

- контроль шини, R /  - перемикання в зондовий режим налагодження,

- перемикання в зондовий режим налагодження,  - очищення внутрішньої кеш-пам'яті,

- очищення внутрішньої кеш-пам'яті,  - вхід переривання в режим SMM - системного управління, INIT - «м'який» скидання процесора, NMI - немасковані переривання, INT - масковані переривання,

- вхід переривання в режим SMM - системного управління, INIT - «м'який» скидання процесора, NMI - немасковані переривання, INT - масковані переривання,  -припинення внутрішньої синхронізації. В процесорах Pentium другого покоління Р54 за допомогою біта регістра TR12 можна змінювати порядок пріоритетів вищеперелічених переривань. Завдяки використанню режиму зондового тестового налагодження за допомогою сигналу R /

-припинення внутрішньої синхронізації. В процесорах Pentium другого покоління Р54 за допомогою біта регістра TR12 можна змінювати порядок пріоритетів вищеперелічених переривань. Завдяки використанню режиму зондового тестового налагодження за допомогою сигналу R /  процесор завершує виконання поточної інструкції і зупиняється. При цьому зовнішній пристрій налагодження можна пов'язати з внутрішніми регістрами процесора. У режим системного управління МП може увійти по сигналу; при вході в цей режим МП зберігає в спеціальній ділянці пам'яті майже всі свої внутрішні регістри. При вході в режим SMM забороняються всі апаратні переривання. Цей режим в основному призначений для реалізації системи управління енергоспоживанням. За допомогою сигналу в процесорі припиняється тактування вузлів, що знижує енергоспоживання в 10 разів. В цьому він не тільки припиняє виконання інструкцій, але і не обслуговує переривання. Подальша подача синхронізації обов'язково повинна супроводжуватися сигналом системного скидання RST. У стан зниженого споживання процесор переходить і при виконанні інструкції HALT, проте в цьому випадку він реагує на всі виникаючі переривання.

процесор завершує виконання поточної інструкції і зупиняється. При цьому зовнішній пристрій налагодження можна пов'язати з внутрішніми регістрами процесора. У режим системного управління МП може увійти по сигналу; при вході в цей режим МП зберігає в спеціальній ділянці пам'яті майже всі свої внутрішні регістри. При вході в режим SMM забороняються всі апаратні переривання. Цей режим в основному призначений для реалізації системи управління енергоспоживанням. За допомогою сигналу в процесорі припиняється тактування вузлів, що знижує енергоспоживання в 10 разів. В цьому він не тільки припиняє виконання інструкцій, але і не обслуговує переривання. Подальша подача синхронізації обов'язково повинна супроводжуватися сигналом системного скидання RST. У стан зниженого споживання процесор переходить і при виконанні інструкції HALT, проте в цьому випадку він реагує на всі виникаючі переривання.

МП Pentium MMX (P55C) орієнтований на мультимедійне, 2D і 3D-графічне застосування. В даному МП реалізована технологія SIMD (одиночний потік команд, множинний потік даних). З метою прискорення процесу мультимедійних додатків до складу команд P55C введено 57 інструкцій для обробки декількох одиниць даних. У складі регістрів використані регістри ММХ0-ММХ7 (насправді в якості регістрів ММХ0-ММХ7 використані регістри з плаваючою комою). Одночасно обробляється 64-розрядне слово може інтерпретуватися як 8 однобайтних, 4 - двобайтних і два - чотирьохбайтних слова. Розмір внутрішньої кеш-пам'яті даного МП збільшено в 2 рази, використовується більш ефективна система пророкування розгалужень, що природно підвищує продуктивність ММХ - процесорів і при виконанні звичайних операцій.

Дата добавления: 2015-10-28; просмотров: 153 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Мікропроцесор 486 DX | | | Мікропроцесор Pentium Pro, Pentium II |