Читайте также:

|

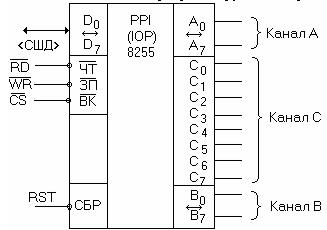

Рис. 2.5.

Схема 8255 (програмований паралельний інтерфейс (ППІ, PPI)) призначена для зв'язку пристроїв вводу/виводу, що працюють у паралельному коді з МП і включає три канали А, В і С. УГЗ ППІ приведено на рис. 2.5. Відповідно до УГЗ схема 8255 має 32 двонаправлених інформаційних виведення: вісім виводів D0-D7, що підключаються до системної шини даних, вісім виводів А0-А7 каналу А, вісім виводів В0-В7 каналу В, вісім виводів С0-С7 каналу С, а також шість керуючих входів. Вхід «скидання» ( ); 2 адресних входи А0 – А1 (підключаються до США); вхід вибору кристала

); 2 адресних входи А0 – А1 (підключаються до США); вхід вибору кристала  ; читання

; читання  ; запису

; запису  .

.

Залежно від комбінації сигналів на керуючих входах через дану схему може передаватися інформація між МП і зовнішніми пристроями в обох напрямках (табл.. 2.1.)

Таблиця 2.1.

Структурна схема програмованого паралельного інтерфейсу (ППІ) представлена на рис.2.6.

Рис. 2.6. Структурна схема ППУ

Відповідно до структурної схемою до складу паралельного інтерфейсу включено три канали А, В, С. Канал А містить два 8-розрядних регістри Рг1 і Рг2. Канал В включає 8-розрядний регістр РгЗ. Канал З містить два 4-розрядних регістра Рг4 і РГ5. Програмований інтерфейс містить також схему буфера даних, яка пов'язує СШД з внутрішньою ШД, регістр управління РгУ (8 розрядів), схему місцевого управління СМУ.

Схема 8255 може працювати в трьох режимах:

• режим 0 - режим асинхронного вводу/виводу одразу ж по 3 каналах;

• режим 1 - режим синхронного вводу або виводу по каналам А і В. Окремі розряди каналу З використовуються для прийому і видачі керуючих сигналів, що забезпечують синхронний ввід та вивід каналів А і В;

• режим 2 - режим двонаправленого вводу/виводу по каналу А.

При надходженні сигналу системного скидання « » обнуляються всі регістри схеми 8255, після чого потрібно знову запрограмувати роботу даної схеми Програмування здійснюється за допомогою керуючого слова, яке записується в регістр РгУ. Структура полів керуючого слова представлена на рис. 2.7.

» обнуляються всі регістри схеми 8255, після чого потрібно знову запрограмувати роботу даної схеми Програмування здійснюється за допомогою керуючого слова, яке записується в регістр РгУ. Структура полів керуючого слова представлена на рис. 2.7.

Рис 2.7. Структура полів керуючого слова

За допомогою ще одного - спеціального керуючого слова можна встановлювати або скидати окремі розряди каналу С. Розряд А7 = 0, А6 - А4-не використовуються, А3-A1 кодують номер розряду каналу С; а0 - визначає, чи треба встановити в 0 чи в 1.

Звернення до схеми ВВ55 може здійснюватися як до інших пристроїв вводу/виводу шляхом дешифрації розрядів адреси А2-А7 чи по командам вводу/виводу (IN-OUT).

Якщо схема працює в режимі 0, то при виконанні операції читання інформації з відповідного буферного регістра (одного з трьох каналів) в момент появи низького рівня керуючого сигналу читання  передається через СШД в МП.

передається через СШД в МП.

При виконанні операції запису при появі низького рівня сигналу  інформація з мікропроцесора передається в один з буферних регістрів, а потім відразу ж у відповідний пристрій вводу/виводу, що підключений до відповідного каналу.

інформація з мікропроцесора передається в один з буферних регістрів, а потім відразу ж у відповідний пристрій вводу/виводу, що підключений до відповідного каналу.

Розглянемо різні режими роботи схеми 8255:

Режим 1 (ввід). Для виконання операції вводу/виводу по каналах А, В необхідно задати в дану мікросхему наступне керуюче слово:

| D3 | x |

У даній ситуації окремі розряди каналу С мають зміст:

· С0 - запит переривання каналу В (ЗПР2)

· C1 - підтвердження прийому даних з каналу В (ППД2)

· С2 - строб-імпульс каналу В ( )

)

· С3 - запит переривання каналу А (ЗПР1)

· С4 - підтвердження прийому даних з каналу А (ППД1)

· С5 - строб каналу А ( )

)

· С6, С7 - вільні, їх можна запрограмувати для підключення третього пристрою вводу/виводу.

Введення даних здійснюється наступним чином: один із зовнішніх пристроїв, що підготував чергову порцію інформації, передає її на відповідні виводи схеми і супроводжує її сигналом  .

.

Після отримання інформації схема 8255 передає у зовнішній пристрій відповідний сигнал (ППД) - підтвердження прийому даних - і формує запит переривання в МП. При обробці цього переривання МП видає команду IN і виробляє низький рівень сигналу  . За цим сигналом з відповідного каналу через СШД в МП передається байт інформації.

. За цим сигналом з відповідного каналу через СШД в МП передається байт інформації.

Режим – 1 (вивід по двох каналах А і В).

Керуюче слово, яке необхідно задати для реалізації режиму виводу, має вигляд:

| D3 | x |

Рис. 2.8.

С4 – С5 в цьому випадку виявляються вільними.

Передача даних з МП в зовнішні пристрої відбувається таким чином: по команді «вивід» інформація з МП через СШД передається в схему ВВ55, де записується у відповідний канал в момент надходження низького рівня сигналу «IN». Отримавши інформацію, канал видає у відповідний зовнішній пристрій сигнал ГТК (готовність каналу). У зовнішньому пристрої по цьому сигналу здійснюється фіксація даних, після чого зовнішній пристрій виробляє відповідний сигнал ПЗД (підтвердження запису даних). Схема ВВ55 відповідає на нього сигналом ЗПР (запит переривання), який надходить в МП, інформуючи його про те, що можна передавати чергову порцію інформації.

Для завдання режиму 2 три старших розряди керуючого слова повинні мати значення 110. Виводи С0-С2 вільні. Використовуючи розряд D0, їх можна запрограмувати на вхід або вихід.

2.4. Програмований послідовний інтерфейс 8251 (універсальний синхронно-асинхронний прийомо-передавач)

Дана мікросхема програмованого послідовного інтерфейсу PSI використовується для обміну інформацією між МП і зовнішніми пристроями, що працюють в послідовному коді. Як правило, її використовують для зв'язку МП з віддаленими терміналами (через модем). Схема 8251 виконує більш складну роботу, ніж 8255. У ній здійснюється перетворення інформації з паралельної форми на послідовну, обрамлення перетвореної інформації шляхом додавання до неї службових даних: стартових, стопових посилок, контрольних бітів і спеціальних байтів синхронізації.

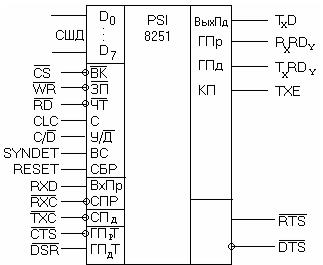

Така мікросхема може працювати в асинхронному режимі з максимальною швидкістю 9,6 Кбіт / с, а в синхронному режимі - 56 Кбіт / с. УГЗ схеми PSI показано на рис. 2.9.

Схема пов’язана з СШД за допомогою 8-ми інформаційних виходів D0-D7, на які надходить або з яких видається паралельний код. Вона має інформаційний вхід послідовного коду - вхід приймача RxD, вихід послідовного коду - XD

.

Рис. 2.9. УГЗ схеми PSI

де:

керуючі входи:

- вибір кристала;

- вибір кристала;

- запис;

- запис;

- читання;

- читання;

CLC - синхронізація;

C/  - керування чи дані;

- керування чи дані;

SD - вид (вибір) синхронізації;

RST - скидання;

– синхронізація приймача;

– синхронізація приймача;

– синхронізація передавача;

– синхронізація передавача;

RxRD - готовність приймача;

TxRD - готовність передавача;

ТXE - кінець передачі.

Сигнали управління модемом:

- готовність приймача терміналу;

- готовність приймача терміналу;

– готовність передавача терміналу;

– готовність передавача терміналу;

– запит приймача терміналу;

– запит приймача терміналу;

– запит передавача терміналу.

– запит передавача терміналу.

Структурна схема PSI приведена на рис. 2.10.

Рис. 2.10. Структурна схема PSI

де:

• БД - буфер даних (який пов'язує СШД МП з внутрішньою ШД) i містіть два регістри Рг1 і Рг2 (вхідній і вихідний).

• ПД - блок передавача, де здійснюється перетворення паралельного коду в послідовний.

• ПР - блок приймача, де здійснюється перетворення послідовного коду в паралельний.

• БУ - блок управління включає регістр режиму РгР, реєстр наказу РгН, реєстр стану РгС, реєстр синхронізації байта Перша і іншого РгС1 и РгС2, схема управління СУ;

• СУМ - схема управління, модемом.

Дана схема, як зазначалось вище, працює в асинхронному або синхронному режимі. Асинхронний режим - режим посимвольного вводу/виводу інформації. Символ може містити від 5 до 8 розрядів. До інформаційних розрядів кожного символу додається службова інформація: біт парності/непарності (ч/н), стартова (t) i степові посилки тривалістю 1, 1,5 і 2 t.

При роботі в синхронному режимі (передача групи символів), кожної посилки містіть 1 або 2 синхронізуючих байта СБ, після чого йдуть інформаційні байти (БД - байт даних) (рис. 2.11.)

| СБ1 | СБ2 | БД1 | БД2 | … | … |

Рис. 2.11.

Програмування даного кристала здійснюється за допомогою керуючих слів режиму та наказу, які слідують в певному порядку після появи сигналу системного скидання RST, який обнуляє всі регістри схеми PSI.

Окремі розряди керуючого слова режиму, які заносяться в регістр режиму, мають наступний зміст: (рис. 2.12.).

Рис. 2.12.

Де: АР - асинхронний режим,

СР - синхронний режим,

Ч - парність,

Н - непарність.

Після надходження сигналу системного скидання RST обнуляються всі регістри схеми, після чого необхідно виконати повторне програмування роботи схеми (рис. 2.13.).

1.Завантажується керуюче слово режиму.

2. Один або два синхробайти (для синхронізації режиму).

3. Керуюче слово наказу.

Після чого можна передавати інформаційні байти.

Рис. 2.13.

Де: АР - асинхронний режим,

УСП - керуюче слово наказу,

УСР - керуюче слово режиму,

КП - кінець передачі.

Окремі розряди керуючого слова наказу мають наступний зміст:

· D0 - дозвіл передачі

· D2 - дозвіл прийому

· D1 - формування сигналу готовності передавача терміналу

· D3 - розрив передачі (якщо 0 - здійснюється нормальна робота, 1 - розрив, на виході передавача низький потенціал)

· D4 - скидання помилок

· D5 - формування сигналу готовності приймача терміналу

· D6 — розряд внутрішнього програмного скидання

· D7 — розряд дозволу пошуку символу синхронізації.

МП за допомогою команди «вводу» може отримати зі схеми 8251 байт її внутрішнього стану, який має три розряди, що фіксують помилки під час роботи:

- D 3 — помилка паритету

- D4 - помилка переповнення

- D5 — помилка кадру (відсутність стопової посилки при роботі схеми в асинхронному режимі).

При виконанні асинхронного вводу поява низького рівня на вході приймача інтерпретується як стартова посилка.

Усередині схеми 8251 є спеціальний лічильник, який підраховує кількість інформаційних біт і визначає момент появи стопової посилки. По завершенні часу, який виділяється для цієї посилки, повинен виробитися сигнал «готовність приймача». Якщо цей сигнал не виробляється, в розряді D5 слова стану з'являється 1.

При синхронному вводі робота схеми починається з пошуку синхробайта.

При цьому прийнята інформація порівнюється з кодами, які зберігаються у відповідних регістрах. При співпадінні інформації виробляється високий потенціал на виході SYNDET, який є двонаправленим, цей сигнал можна використовувати як сигнал ЗБР. Тільки після вироблення цього сигналу МП почне приймувати інформацію зі схеми ВВ51.

Дата добавления: 2015-10-28; просмотров: 599 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Мікропроцесор AMD-K6 | | | Програмований контролер переривання 8259А |