Читайте также:

|

Апаратні переривання забезпечують своєчасну реакцію ПК на події, що відбуваються асинхронно стосовно реалізованої програмі шляхом реєстрації запитів переривання, що надходять з контролерів переривань на відповідні входи МП, а саме вхід немаскованих зовнішніх переривань NMI і входи маскуються зовнішніх переривань.

Немасковані переривання обробляються МП незалежно від стану прапора (ознаки) дозволу переривання регістра ознак F. Ці переривання надходять на вхід NMI або на вхід SMI в МП, що підтримує режим системного управління. Сигнал на вхід NMI може надходити від схем контролю паритету ОП, або по лінії IOCHK шини ISA або  шини PCI. Якщо під час обробки немаскованого переривання знову виникає сигнал NMI, то вкладеного переривання не буде, так як повторний виклик обробки таких переривань можливий тільки після виконання команди повернення RET. Переривання SMI виробляється схемами управління режимом енергоспоживання. Ці переривання мають найвищий пріоритет і обслуговуються інакше, ніж класичні переривання. Обробка немаскованих переривань може заборонятися інструкцією Є.І. та вирішаться - DI. Масковані переривання обслуговуються спеціальним контролером, який може обробляти тільки одне переривання, одним із завдань якого є вибір найбільш пріоритетного з виниклих запитів і передача інформації про вибраний запиті через свій вихід INTA на відповідний вхід МП. Якщо переривання дозволено, МП входить в машинний цикл підтвердження переривання. У цьому циклі в стек записується інформація трьох регістрів МП: регістра F, покажчика команд IP і кодового сегмента CS. Тим самим у стеці зберігаються точка повернення до поточної програмі після завершення програми, яка буде обслуговувати виникле переривання. Як програмований контролер переривань використовується схема, програмно сумісна з контролером типу 8259А. Цей контролер вимагає два машинних циклу обробки переривань INTA. При цьому процесори 80х86 для передачі одного байта покажчика номера входу в таблицю переривань використовують другий цикл. Цей байт є покажчиком одного з можливих 256 типів переривань. Кожен номер переривання пов'язаний зі своїм вектором, що представляє собою подвійне слово, є адреса входу в програму, яка буде обробляти відповідне переривання. Будь-яка процедура обробки переривання завершується інструкцією повернення RET, по якій з стека відновлюються автоматично збережені регістри F, CS, IP, і МП зможе продовжувати виконання перерваної поточної програми, починаючи з команди, наступної за тією після якої почала виконуватися обслуговуюча програма.

шини PCI. Якщо під час обробки немаскованого переривання знову виникає сигнал NMI, то вкладеного переривання не буде, так як повторний виклик обробки таких переривань можливий тільки після виконання команди повернення RET. Переривання SMI виробляється схемами управління режимом енергоспоживання. Ці переривання мають найвищий пріоритет і обслуговуються інакше, ніж класичні переривання. Обробка немаскованих переривань може заборонятися інструкцією Є.І. та вирішаться - DI. Масковані переривання обслуговуються спеціальним контролером, який може обробляти тільки одне переривання, одним із завдань якого є вибір найбільш пріоритетного з виниклих запитів і передача інформації про вибраний запиті через свій вихід INTA на відповідний вхід МП. Якщо переривання дозволено, МП входить в машинний цикл підтвердження переривання. У цьому циклі в стек записується інформація трьох регістрів МП: регістра F, покажчика команд IP і кодового сегмента CS. Тим самим у стеці зберігаються точка повернення до поточної програмі після завершення програми, яка буде обслуговувати виникле переривання. Як програмований контролер переривань використовується схема, програмно сумісна з контролером типу 8259А. Цей контролер вимагає два машинних циклу обробки переривань INTA. При цьому процесори 80х86 для передачі одного байта покажчика номера входу в таблицю переривань використовують другий цикл. Цей байт є покажчиком одного з можливих 256 типів переривань. Кожен номер переривання пов'язаний зі своїм вектором, що представляє собою подвійне слово, є адреса входу в програму, яка буде обробляти відповідне переривання. Будь-яка процедура обробки переривання завершується інструкцією повернення RET, по якій з стека відновлюються автоматично збережені регістри F, CS, IP, і МП зможе продовжувати виконання перерваної поточної програми, починаючи з команди, наступної за тією після якої почала виконуватися обслуговуюча програма.

Даний контролер 8259А являє собою схему, яка має 8 входів запитів переривання і 1 вихід, на який надходить найпріоритетніший з виниклих запитів.

Для вибору найпріоритетнішого запиту схема може реалізовувати одну з чотирьох дисциплін обслуговування переривань. Для розширення числа запитів можна використовувати каскадне з'єднання декількох схем, причому одна з них буде ведучою, решта веденими. Максимально можна побудувати систему, що каскадується, яка обслуговуватиме 64 переривання, і включатиме 8 керуючих схем і 1 керовану.

Рис. 2.14. УГЗ контролера 8259А Рис. 2.15. Функціональна схема

контролера 8259А

Відповідно до УГЗ контролер (рис. 2.14.) має 8 двонаправлених виходів даних D0-D7, що підключаються до СШД, 8 входів запитів переривань IRQ, вибір кристала CS,  – запис,

– запис,  – читання, А0 – молодший розряд адреси,

– читання, А0 – молодший розряд адреси,  - підтвердження переривання,

- підтвердження переривання,  - керована мікросхема, ITN – вихід запита переривання в МП, три двонаправлені виходи каскадування CAS1 – CAS3 (використовуються як виходи у провідному контролері і як входи у керованих контролерах).

- керована мікросхема, ITN – вихід запита переривання в МП, три двонаправлені виходи каскадування CAS1 – CAS3 (використовуються як виходи у провідному контролері і як входи у керованих контролерах).

Функціональна схема контролера, представленого на рис. 2.15, містить:

· БД - буфер даних, який пов'язує восьмирозрядну СШД з внутрішньою восьмирозрядною ШД. Виходи буфера мають 3 стани.

· БПР – блок переривань, який включає восьмирозрядний регістр переривань Pr1 (1) (він запам'ятовує запити переривань), восьмирозрядний регістр маски Pr2 (2 (за допомогою маски можна забороняти деякі переривання), блоку (3), регістру обслуговування переривань (4). Інформація, що міститься в Pr1, аналізується БПР з урахуванням маски, вибирається найбільш пріоритетний запит із зафіксованих і записується в регістр обслуговування переривань (4).

·  СУВВ – схема управління вводом/виводом. Шляхом аналізу вхідних керуючих сигналів, за допомогою даної схеми забезпечується надходження інформації з МП при низькому сигналі запису

СУВВ – схема управління вводом/виводом. Шляхом аналізу вхідних керуючих сигналів, за допомогою даної схеми забезпечується надходження інформації з МП при низькому сигналі запису  , який з'являється при виконанні команди OUT. Така інформація записується з МП в схему при її початковій ініціалізації (при програмуванні режимів робота схеми); ініціалізація виконується за допомогою слів наказу (слів початкової установки - СНУ) і керуючих слів операції (УСО). Виконуючи команду "ввід" (IN), під час якої з'являється низький сигнал читання

, який з'являється при виконанні команди OUT. Така інформація записується з МП в схему при її початковій ініціалізації (при програмуванні режимів робота схеми); ініціалізація виконується за допомогою слів наказу (слів початкової установки - СНУ) і керуючих слів операції (УСО). Виконуючи команду "ввід" (IN), під час якої з'являється низький сигнал читання  , можна прочитати в МП інформацію з регістра стану (РгС) даного кристала, при високому сигналі ВК вибір кристала CS виходи переводяться в третій стан.

, можна прочитати в МП інформацію з регістра стану (РгС) даного кристала, при високому сигналі ВК вибір кристала CS виходи переводяться в третій стан.

· БРУ – блок регістрів і управління, включає три Pr1 СНУ, три Pr2 УСО, регістр стану РгС), формувач коду (ФК) операції команди CALL 11001101, схему управління каскадуванням СУК (управляє роботою провідної і керованої схемами).

Програмування режиму роботи схеми ВН59 здійснюється передачею по команді OUT з МП кількох СПУ (ICW) і керуючих слів операцій УСО (OCW). Структура слів СПУ показана на рис. 2.16.

Рис. 2.16. Структура слів СПУ

СПУ1 – має розташовуватися в ОП за парною адресою (А0 = 0) і містить наступні поля:

· D1 – визначає кількість контролерів (D1 = 1 – один контролер, D1 = 0 – кілька провідних і керованих контролерів);

· D3 – переривання по рівню (D3 = 1) або по фронту;

· D0 – ознака використання СПУ4.

СПУ2 – обов'язково розташовується за непарною адресою (А0 = 1) і задає початковий номер вектора переривання.

Слова початкової установки (СНУ або СПУ) використовуються тільки в тому випадку, якщо використовуються кілька контролерів.

Слово СНУ4 визначає режим роботи контролера переривань (його використання при початковій ініціалізації обов'язково). В цьому слові біти 7-5 не використовуються.

· Біт D4 – визначає наявність вкладених пріоритетів;

· Біт D3 - наявність буферного режиму;

· Біт D2 - 1 - для провідного, 0 - для керованого;

· Біт D1 - дозвіл автоматичного завершення переривання, при якому по закінченні обслуговування запиту біт маски не скидається.

Після ініціалізації подальше управління роботою контролера переривань здійснюється за допомогою слів УСО керуюче слово обміну (OCW). Таких слів передбачено три. На відміну від СНУ вони видаються МП в будь-якому порядку, коли це потрібно програмі.

Слово УСО1 - маска запитів, одиничне значення відповідного біта в цьому слові маскує запит.

Друге керуюче слово УСО2 використовується для управління пріоритетами переривань. Біт D7 визначає можливість отримання пріоритетів. Отримуючи запити від пристроїв введення - виведення, контролер переривань визначає (як зазначалося вище), який із запитів володіє найвищим рівнем пріоритету.

Рівні пріоритетів IRQ7-IRQ0 знаходяться завжди в певному співвідношенні, яке прийнято називати статусом рівнів пріоритету. Форма завдання статусу рівнів пріоритету є пріоритетне кільце. Структура пріоритетів, яка встановлюється за умовчанням, визначає фіксований порядок від вищого для входу IRQ0 (вершина пріоритетного кільця) до нижчого IRQ7 (дно пріоритетного кільця).

Ставлячи положення дна кільця, можна визначати пріоритет кожного входу контролера переривань. Контролером передбачено кілька програмних способів завдання дна пріоритетного кільця. встановивши розряд D7 = 1, можна задати режим циклічної обслуговування переривань, при якому обслуговуваному пристрію присвоюється низький пріоритет (дна кільця); режим обслуговування переривань, при якому за допомогою трьох молодших розрядів цього слова (поле L) задається входом IRQ (дно пріоритетного кільця) з найнижчими пріоритетом. Якщо розряд D5 = 1, то при наявності в розряді D6 одиниці поле L визначатиме номер скидається розряду в регістрі маски після закінчення обслуговування переривань. Слово УСО3 використовується для оперативного управління контролером переривань. В цьому слові можна встановити дисципліну обслуговування переривань, що використовує режим опитування: опитуються всі УВВ і вибирається той з них, який в ланцюжку стоїть найближче до МП і виробив переривання; D6,D5 – режим спеціального маскування (11 - встановити спеціальне маскування, 10 - скинути спеціальне маскування, 0Х - спеціальне маскування не використовувати (тобто, застосовується, коли немає спеціального маскування)); D2 – зберегти або скинути режим опитування (1 - зберегти, 0 - скинути). За допомогою бітів D1 і D0 можна прочитати в МП вміст регістра запиту переривання і регістра обслуговування переривання: 0Х - не використовується 11 - регістр обслуговування переривання, 10 - регістр запиту переривання.

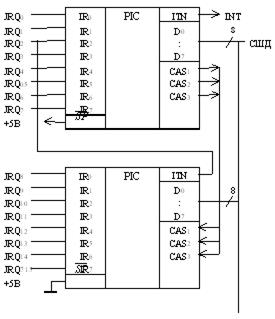

В сучасних МПС, починаючи з архітектури PC AT використовується система переривань, що складається з двох контролерів 8259А (рис. 2.17.). Перший з цих контролерів є ведучим (головним), другий веденим (підлеглим). Така система переривань може обслужити 15 запитів переривання.

Рис. 2.17.

У ведучому вихід SP підключається до +5 В, у веденому - заземлюється. Виводи каскадування в першому являють собою виходи, у другому - входи. Вихід запиту переривань підпорядкований INT під'єднується до входу IRQ2 ведучого. У такій системі розподіл пріоритетів буде виглядати наступним чином: IR0, IR1, IR8, IR9, IR10, IR11, IR12, IR13, IR14, IR15, IR3, IR4, IR5, IR7. Ведучий контролер обслуговує запити 0, 1, 3 - 7, ведений контролер обслуговує запити 8 - 15. При цьому використовується вкладеність пріоритетів. Запити другого контролера 8 - 15 зі своїм рядом відбувають пріоритетів вклинюються між першим і третім запитами ведучого контролера, пріоритет яких також зменшується з ростом номера.

В МПС, що використовують 286 МП і вище, застосовуються такі стандартні призначення входів визначення запитів переривання:

· IQ0 – таймер (вектор 08H);

· IQ1 - клавіатура (вектор 09H);

· IQ2 - підключення до входу INT керованого контролера;

· IQ3 - другий послідовний порт (вектор 0BH):

· IQ4 - перший послідовний порт (вектор 0CH);

· IR5 - другий паралельний порт (вектор 0DH);

· IR6 - контролер гнучкого диска (вектор 0EH);

· IR7 - перший паралельний порт (вектор 07H);

· IR8 - вхід RTC – годинника реального часу (вектор 70H);

· IR9 - резерв (вектор 71H);

· IR10 - резерв (вектор 72H);

· IR11 - резерв (вектор 73H);

· IR12 - резерв (вектор 74H);

· IR13 - арифметичний співпроцесор (вектор 75H);

· IR14 - контролер жорстких дисків (вектор 76H);

· IRQ15 - резерв (вектор 77H);

В МПС, що використовують 386-й, 486-й МП, застосовується схема контролера переривань 8259А, яка представляє собою каскадне включення двох схем 8259А. Для реалізації системи переривань в МПС використовують МП Pentium, Pentium Pro, Pentium є вбудований мікропроцесор - контролер переривань (APIC - Advanced Programmable Interruption Controller).

Дата добавления: 2015-10-28; просмотров: 259 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Програмований паралельний інтерфейс 8255 | | | Контролер прямого доступу до пам’яті 8237А |