Читайте также:

|

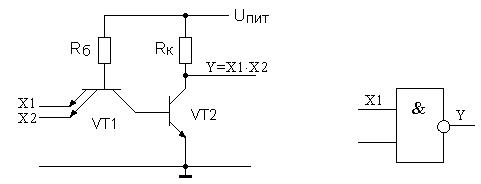

В ЛИС, выполненных по технологии ТТЛ, в качестве базового элемента применяется многоэмиттерные транзисторы (МЭТ). МЭТ отличается от обычного транзистора тем, что имеет несколько эмиттеров, расположенных на кристалле так, чтобы взаимодействие между ними было исключено. Например, упрощенную схему ТТЛ ЛИЭ И-НЕ можно представить в следующем виде (рис. 1-11а):

а) б)

Рис. 1-11

Если на одном или обоих эмиттерах транзистора VT1 будет низкий уровень напряжения (логический 0), то транзистор VT1 закрыт и, следовательно, ток базы транзистора VT2 равен нулю, а напряжение на его коллекторе будет практически равно Uпит., что соответствует уровню логической 1. Если на обоих эмиттерах транзистора VT1 будет высокий уровень напряжения (на обоих эмиттерах логические 1), то транзистор VT1 открыт и ток базы транзистора VT2 не равен нулю. Значение тока базы выбирается таким, чтобы транзистор вошел в насыщение. В этом случае напряжение на его коллекторе близко к нулю, что соответствует уровню логического 0. На выходе ТТЛ ЛЭ могут использоваться сложные инверторы и повторители. На рис. 11б показано условное графическое обозначение ЛИЭ И-НЕ.

Напряжение питания Uпит для микросхем ТТЛ равно Uпит = + 5 В. Уровень логической единицы U1 ≥ 2,4 B, а уровень логического нуля Uo ≤ 0,4 B.

В ЭСЛ в качестве базового элемента используется дифференциальный усилитель (рис. 1-12). В одно плечо усилителя включается несколько транзисторов, образующих логический элемент ИЛИ. Высокое быстродействие ЭСЛ достигается тем, что транзисторы в них работают в ненасыщенном (линейном) режиме. Благодаря этому исключается влияние времени выхода транзистора из насыщения на быстродействие. У ТТЛ оно, в основном, определяет время переключения. На выходе ЛИЭ имеется повторитель, что обеспечивает быстрый перезаряд емкости нагрузки (из-за низкого Rвых повторителя). Обычно ЛИЭ имеют прямые и инверсные выходы (парафазный выход). Уровень логической еди-

а) б)

Рис. 1-12

ницы равен U1 = - 0,9 B, а уровень логического нуля Uo = - 1,8 B. Напряжение питания Uпит равно для микросхем ЭСЛ 500 серии Uпит = - 5,2 В, для микросхем 1500 серии Uпит = - 4,5 В.

В КМОП ЛЭ используются ключевые схемы на МОП транзисторах, включенных параллельно если организуется элемент ИЛИ и последовательно, если организуется элемент И. В отличии от ТТЛ схем в качестве нагрузочных сопротивлений у транзисторов применяются так же МОП транзисторы. Благодаря этому упрощается процесс изготовления микросхем. Например, базовый двухвходовый элемент И-НЕ имеет вид (рис. 1-13):

Рис. 1-13

При высоком уровне сигнала на входах X 1 и (X 1 = X 2 = 1) транзисторы VT 1 и VT 2 размыкаются (сопротивление высокое) а VT 3 и VT 4 замыкаются (сопротивление низкое) и на выходе ЛИЭ напряжение близкое к нулю (Y =0). Если хотя бы один из входных сигналов ноль, а второй высокий, то один из транзисторов VT 1 и VT 2 замыкаются, а один из транзисторов VT 3 и VT 4 размыкается и на выходе ЛИЭ напряжение близкое к U пит. Напряжение питания современных КМОП ЛИЭ может изменяться в диапазоне 1,5…15 В. Поэтому значения логических уровней нормируется в долях U пит.

Дата добавления: 2015-07-21; просмотров: 110 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Цифровые интегральные логические элементы | | | МИНИМИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ |