|

Читайте также: |

Спільними зусиллями компаній IBM і Motorola був розроблений 64-розрядний RISC-МП РС 620, який зберігає програмну сумісність з попередньою 32-розрядної моделлю РС 604, має продуктивність на 40% вище для операцій цілочисельної арифметики і на 100% - для операцій з плаваючою комою. В даному МП є спеціальний біт в слові стану, який визначає розрядність виконуваних програм. У 32-розрядному режимі використовується молодша половина 64-розрядних регістрів РС 620, що відповідає особливостям розрядності процесора РС 604, а значить забезпечує програмну сумісність з попередньою моделлю. В РС 620 шина адреси має 40 розрядів, завдяки чому фізичний простір, що адресується доведено до одного терабайта, а віртуальний простір - до 1 гектабайта (280).

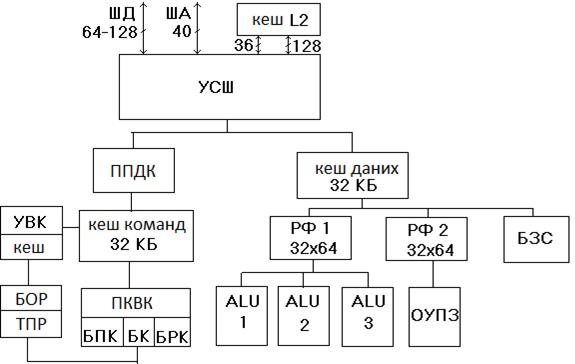

Структурна схема МП РС620 показана на рис. 3.4.

Рисунок 3.4. Структурна схема РС620

Особливість даного МП полягає в тому, що кеш-пам'яті другого рівня можна підключати до системної шини RISC-процесора; роздільні кеш-пам'ять для даних і кеш-пам'ять для команд по 32КБ; ППДК - пристрій попереднього дешифрування команд; блок завантаження-збереження;

Виконавчий пристрій, що включає:

• 3 конвеєра арифметики цілих чисел ALU1-ALU3;

• РОНи, пов'язані з ними (регістровий файл 32х64), і буфера перепризначення;

• Конвеєр арифметики плаваючою точкою ОУПЗ і регістри файлу 32х64, з ним пов'язані.

Пристрій попередньої дешифрування команд (ППДК), пристрій вибірки команд (ПВК), що включає кеш-пам'ять адрес переходу, блок обробки розгалужень (БОР), таблиця передбачення розгалужень (ТПР) 4 буфера, пристрій координації виконання команд (ПКВК), що включає: БК - буфер команд, БПК - буфер перепризначення команд, БРК - буфер розподілу команд.

В даному МП використовують механізм динамічного передбачення розгалуження. Він реалізується за допомогою блоку БОР і кеш-пам'яті адрес переходів. З блоком БОР пов'язана спеціальна таблиця ТПР. Ця таблиця має 256 рядків, завдяки чому вірогідність правильного передбачення розгалуження доведена до 0,9. У пристрої ППДК до кожної команди додається спеціальна 7-бітова ознака, за допомогою якої спрощується процес угруповання команд. Команди, зчитані з кеш-пам'яті команд, накопичуються в БК, а потім їх у міру готовності направляють до одного з виконавчих пристроїв. Після реалізації команд вони накопичуються в БПК, завдяки чому порядок їх видачі буде відповідати порядку їх надходження.

Особливість даного МП полягає в тому, що в ньому апаратно реалізована операція добування квадратного кореня з плаваючою точкою. Шинний інтерфейс забезпечує підтримку зовнішньої кеш-пам'яті L2. Ця пам'ять може мати обсяг до 128 МБ і функціонувати на тактовій частоті RISC-процесора РС 620, на частотах в 2 і 4 рази менше. Даний МП створювався для мультипроцесорних систем. СШ дозволяє підключати до 4 МП. Пропускна здатність цієї шини - 100 Мбіт/с. Унікальною особливістю цього МП є можливість програмного перемикання режимів адресації (Intel/Motorola) завдяки чому можна в ОС Unix виконувати Windows програми.

Дата добавления: 2015-10-28; просмотров: 131 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| RISC-процесор Alpha 21164 компанії DEC | | | RISC-процесор MIPS-10000 |