Читайте также:

|

СУЧАСНІ ЗАСОБИ ПРОЕКТУВАННЯ ЦИФРОВИХ СИСТЕМ

Виконала:

студентка групи ДА-11

Казаченко О.Д.

Київ 2013

Мета роботи

· ознайомлення з інтерфейсом і принципами роботи системи проектування цифрових схем;

· засвоєння основних понять мови VHDL, загальної структури опису цифрового пристрою, методики формування вхідних даних;

· побудова простіших поведінкових моделей, описаних за допомогою паралельних операторів безумовного призначення значень сигналам, і перевірка правильності їх роботи.

Короткі теоретичні відомості

· булеві функції, таблиці істинності, логічні вентилі («Додаток А»);

· засоби опису комбінаційних схем у вигляді систем булевих рівнянь у мові VHDL (скалярні сигнали типу bit, паралельний оператор безумовного призначення значення сигналу) [1,2];

· принципами роботи у пакеті САПР цифрових схем [5].

Структура VHDL описания и типы операторов

объявление signal

операторы безусловного, условного и выборочного присваивания значения сигналу

оператор вызова процедуры

оператор вызова компонента

process (предложение)

generate (предложение)

block (предложение)

assert (оператор сообщения)

объявление variable

оператор вызова процедуры

присваивание значения variable

присваивание значения signal

wait-оператор

операторы: if, case, loop, next, exit, return, null, assert

VHDL – язык описания параллельных процессов.

Параллельными процессами описываются блоки, которые работают параллельно друг с другом во времени. Внутри каждого параллельного блока от его начала до конца время может увеличивается только последовательно.

Операторы являются исполнительными единицами кода. Последовательные операторы выполняются в том порядке, в котором они расположены внутри параллельного процесса. Выполнение параллельных операторов не зависит от порядка их записи. Каждый такой оператор выполняется каждый раз, когда один или несколько из его входных сигналов изменяет свое значение. Изменение значения сигнала называется событием.

Следует обратить внимание на то, что некоторые операторы могут выступать в качестве как параллельных, так и последовательных. Например, вызов процедуры. Как параллельные они будут работать в том случае, если будут записаны в виде отдельных элементов структурной модели, как последовательные, если будут записаны внутри параллельного оператора, например, такого, как process. Последовательные операторы могут располагаться только внутри параллельных операторов.

Сигналы

Сигналы используются для описания соединения между элементами схемы. Сигнал связан с понятием времени. Он может измениться только тогда, когда процесс приостановится и ожидает следующего изменения входных сигналов. Для связывания параллельных операторов могут использоваться только сигналы. Порты, которые объявлены в entity, являются сигналами, а аргументы подпрограмм могут быть как сигналами так и переменными.

Типы сигналов:

bit – скалярный битовый сигнал;

bit_vector – векторный битовый сигнал.

Примеры:

bit_vector (7 downto 0); -- убывающий диапазон

bit_vector (7 to 10); -- возрастающий диапазон

В обозначении любого диапазона слева всегда указывается старший разряд, а справа– младший.

std_logiс - поддерживает многозначную логику и функции разрешения (определения результирующих значений) сигналов в монтажных соединениях.

std_logiс_vector - поддерживает многозначную логику и функции разрешения сигналов в монтажных соединениях для векторных сигналов.

Завдання

3.1) Ознайомтесь з теоретичними відомостями.

3.2) Виписати функції Ф1 і Ф2 за варіантом завдання. Номер варіанту відповідає номеру студента у списку групи. У таблиці 1.1 вказано номери функцій Ф1 і Ф2 від трьох змінних {a, b, c} у переліку логічних функцій:

1. Ф1(a, b, c) = (a v b)’ & c;

| a | b | c | Ф1 |

4. Ф2(a, b, c) = a & b & c v (c)’ & a;

| a | b | c | Ф2 |

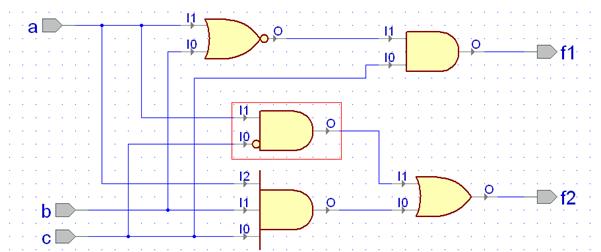

3.3) Намалювати схему у вигляді принципової вентильної схеми згідно рис.1.1. Базис реалізації довільний. Заповнити вручну таблицю істинності схеми для подальшого порівняння з результатами комп’ютерного моделювання.

Рис. 1.1. Загальний вигляд досліджуваної ЦС

3.4) Описати розроблену схему на мові VHDL за допомогою паралельного оператора безумовного призначення у вигляді булевих рівнянь з використанням скалярних сигналів типу bit.

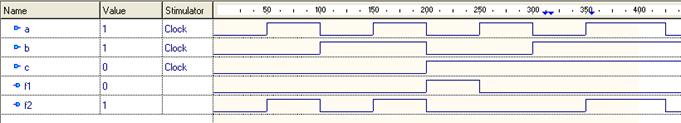

3.5) Для проведення моделювання цифрової схеми на її входи необхідно подати N=23=8 різних логічних наборів вхідних сигналів. Нехай тривалість тактового імпульсу буде 50 у.о., тоді час моделювання має бути більше ніж 50 * 8 = 400 у.о. Для завдання двійкового коду {a, b, c} = { (0,0,0),..,(1,1,1) } (розряд а - молодший) на входи ЦС зручно подати послідовності вхідних сигналів, що зображено на рис.1.2.

Рис. 1.2. Часові діаграми для вхідних логічних сигналів

Висновок

У даній лабораторній роботі, ми пригадали, як проектуються цифрові схеми на мові VHDL, створили схему, яка реалізує, задані варіантом функції. Для цих функцій склали таблицю істиності з урахуванням всіх можливих варіантів на три входи. Наглядно побачили принцип роботи схеми на часовій діаграмі сигналів, подаючи сигнали на вхід таким чином щоб за мінімальний час 400 нс перебрати всі можливі варіанти. Для описання схеми використовували скалярні сигнали типу bit.

Дата добавления: 2015-10-28; просмотров: 134 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Русское ударение | | | Текст програми і результати моделювання у табличній формі і у формі часових діаграм |