Читайте также:

|

· IC is added to instruction cycle to accommodate interrupts

· Processor checks for interrupt

· Indicated by an interrupt signal if interrupts are pending (I/O module sends an interrupt request signal to the processor when the external device becomes ready to be serviced).

· If no interrupt, fetch next instruction

· If interrupt pending:

ü Suspend execution of current program

ü Save context

ü Set PC to start address of interrupt handler routine

Process interrupt

26. In the diagram “Program Flow Control” find … Interrupts are provided primarily as a way to improve processing efficiency. Program Flow Control is an abstraction (some sort of virtual operations) at the set of all possible sequences of execution in the program. Program Flow Control is an abstraction (some sort of virtual operations) at the set of all possible sequences of execution in the program. 1, 2 and 3 – code segments refer to sequences of instructions that do not involve I/O. The WRITE calls are calls to an I/O program that is a system utility and that will perform the actual I/O operation. The I/O operation consists of three sections: 4 – a sequence of instructions which prepare for the operation. I/O command – the actual I/O command. 5 – a sequence of instructions which complete the operation. The user’s program doesn’t have to contain any special code to accommodate interrupts; the processor and the operating system are responsible for suspending the user’s program and then resuming it at the same point.

27. How many techniques of I/O … Three I/O Techniques: Programmed I/O. With the programmed I/O data is exchanged between the CPU and I/O module. The CPU executes a program that gives it direct control of the I/O operation, including sensing device status, sending a read or write command and transferring data. Interrupt-driven I/O. With interrupt—driven I/O, the CPU issues an I/O command, continues to execute other instructions, and is interrupted by I/O module when the latter has completed work. Direct Memory Access (DMA). DMA permits to the I/O module and main memory exchange data directly without CPU involvement.

28. Describe the Direct Memory Access technique. CPU initializes the DMA by sending the following information through Data Register:

the starting address of the Memory block;

the word count (number of words in this block);

type of operation (Read or Write);

a control bit to start the DMA transfer.

After it CPU stops communicating with DMA Controller unless it (CPU) receives an interrupt signal or needs to check how many words have been transferred.

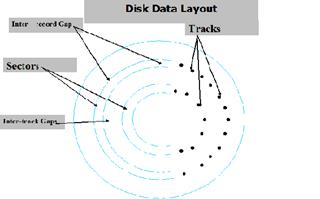

57. Describe the typical Disk data layout 29. Draw a scheme of DMA Transfer

30. Which approaches can be taken… Multiple Interrupts – Sequential. This approach is nice and simple, as interrupts are handled in strict sequential order. The drawback of this approach is that it doesn’t take into account relative priority or time critical needs. Multiple Interrupts – Nested. This approach is to define priorities for interrupts and to allow an interrupt of higher priority (“estate”) to cause a lower-priority interrupt handler to be itself interrupted. Example.

Consider a system with 3 I/O devices:

a printer (priority 2);

a disk (priority 4);

a communication line (priority 5)

Let user program begins at t = 0. At t = 10, a printer interrupt occurs, user information is placed on the stack, and execution continues at the printer interrupt service routine (ISR). While this routine is still executing, at t = 15, a communication interrupt occurs. Since communication line has higher priority, the interrupt is honored, the printer ISR is interrupted.

31. What is the interconnection structure, and by which factors is it determined?

The way of connecting the various modules is called the interconnection structure. The interconnection structure is determined by character of exchange operations, which are specific for each module.

32. List the types of exchanges (input and output)

Memory: a memory module will consists of N words of equal length. Each word is assigned a unique numerical address (0, 1, …, N-1). A word of data can be read from or written into the memory. The nature of the operations is indicated by READ or WRITE control signals. The location for the operation is specified by an address.

I/O Module: It’s functionally similar to the memory (from internal point of view). There are two operations READ and WRITE. Further, an I/O module may control more than one external device. We can refer to each of the interfaces to an external device as a port and give each a unique address (e.g., 0, 1, 2.,…, M-1). In addition, there are external data paths for the input and output of data with an external device. Finally, an I/O module may be able to send interrupt signals to the CPU.

CPU: CPU reads in instructions and data, writes out data after processing, and uses control signals to control the overall operation of the system. It also receives interrupt signals.

· Memory to CPU: The CPU reads an instruction or unit of data from memory.

· CPU to Memory: The CPU writes a unit of data to memory.

· I/O to CPU: The CPU reads data from I/O device via an I/O module.

· CPU to I/O: The CPU sends data to the I/O device.

· I/O to or from the Memory: For these two cases, an I/O module is allowed to exchange data directly with memory, without going through the CPU, using DMA.

33. What kind of buses does the System Bus include?

A system bus consists of from 50 to 100 separate lines, which can be classified into three functional groups: data, address and control lines (power lines are usually omitted).

The data lines provide a path for moving data between system modules. Number of lines is referred as WIDTH of the data bus

Address Bus width determines maximum memory capacity of the system. Identify the source or destination of data. Used to address as the Main Memory, so I/O ports.

Control Bus. Is used to control the access to and the use of the data and address lines. Control and timing information (indicate validity of data and address information)

· Memory read/write signal

· Interrupt request

Typical control lines include:

q Memory Write

q Memory Read

q I/O Write

q I/O Read

q Transfer ACK

q Bus Request

q Bus Grant

q Interrupt request

q Interrupt ACK

q Clock

q Reset

34. What do we call the width of a bus?

Width of the data bus (the number of lines determines how many bits can be transferred at a time). Width determines maximum memory capacity of the system.

35. What operation does the control signal “I/O read” set?

I/O Read: Causes data from the addressed I/O port to be placed on the bus

The operation of any bus is as follows:

If one of the modules “wishes” to send data to another, it must do two things:

1. Obtain the use of the bus;

2. Transfer data through the bus.

If one of the modules “wishes” to receive data from the other module it must do:

1. Obtain the use of the bus;

2. Send request to the other module, by putting the corresponding code on the address lines after formation signals on the certain control lines.

36. What problems may arise, when only one (single) bus is used in a computer system?

· Lots of devices on one bus leads to:

§ Propagation delays (задержки распространения).

o Long data paths mean that co-ordination of bus use can adversely affect (неблагоприятно сказываться) performance (dynamic characteristics become worse).

o If aggregate data transfer approaches bus capacity the system’s work may become unreliable.

· Most systems use multiple buses organised by hierarchy principle to overcome these problems

37. Give examples of using multiple bus structures in computer systems and explain necessity of including each…

The use of multiple buses, each of which may connect only some certain modules (Expansion Bus, High-Speed Bus)

38. List and describe main generic types of buses.

Dedicated

§ Separate data & address lines

Multiplexed

v Shared Lines

v Address valid or Data valid control lines

v Advantage – fewer lines

v Disadvantages

q More complex control

q Reduction in performance

Дата добавления: 2015-10-26; просмотров: 121 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| The Computer Performance (CP) is determined by number of certain (well known) operations per time unity. | | | Enumerate elements of Cache Design. |