Читайте также:

|

Мультиплексор – это устройство в котором в зависимости от управляющего входа осуществляется передача информации с одного из нескольких входов на выход.

В схемах мультиплексоров используются электронные ключи, замыкание которых производится под действием управляющих сигналов, приходящих например, с дешифратора. Часто функции дешифратора и ключа объединены в одном элементе И.

Разрядность n управляющего сигнала определяет количество входов 2n с которых мультиплексор позволяет осуществлять прием информации.

Наличие разрешающего входа расширяет возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Этот вход используется также для наращивания разрядности.

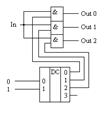

Демультиплексор – функции демультиплексора противоположны функциям мультиплексора. Демультиплексор имеет один информационный вход D, несколько выходов и осуществляет коммутацию сигнала на один из выходов схемы, адрес которого установлен на адресных шинах.

Демультиплексор – это функциональный узел, осуществляющий коммутацию информации с одного входа на один из нескольких выходов. Демультиплексоры в виде самостоятельных ИС не изготавливаются, т.к. их функции могут выполняться дешифратором, имеющим хотя бы один вход разрешения, который используется как информационный вход

Демультиплексор используется в многоканальных цифровых устройствах для передачи информации в различные каналы. Он представляет собой дешифратор ко входам которого подключены 2n цифровых электронных ключей (n-число входов дешифратора). Информационные входы ключей объединены и являются информационным входом демультиплексора.

При поступлении на входы дешифратора 2-х "0", появляется "1" на выходе y1', открывающая верхний ключи цифровая информация с входа I проходит в канал y1. Таким образом, изменяя код на входе ДШ можно управлять передачей входной информации в нужные каналы. В качестве демультиплексоров могут использоваться дешифраторы со входами разрешения (E), используя Е как информационный вход.

8. Сумматоры: основные определения, классификация. Принцип работы на примере одноразрядного полусумматора.

Сумматор — логический операционный узел, выполняющий арифметическое сложение двоичных кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное.

Однорозрядный сумматор – это сумматор который выполняет сложение трех одноразрядных чисел – двухслогаемых а и b c учетом переноса р из боле младшего разряда в более старший.

По числу входов и выходов одноразрядных двоичных сумматоров различают:

четвертьсумматоры, характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом - перенос в следующий (старший разряд);

полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом - перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на:

последовательные, в которых обработка чисел ведётся поочередно, разряд за разрядом, на одном и том же оборудовании;

параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование

В зависимости от способа обработки чисел различают последовательные и параллельные сумматоры. Последовательные сумматоры строятся на основе одноразрядной суммирующей схемы. В таких устройствах сложение двух чисел производится поразрядно, последовательно во времени. Параллельные сумматоры комбинационного типа представляют собой композиции одноразрядных суммирующих схем, причем обработка чисел в таких устройствах осуществляется одновременно во всех разрядах. Логическое проектирование в этом случае сводится к синтезу одноразрядных сумматоров и организации цепей переноса в соответствии с заданными требованиями на быстродействие.

На рис.1 показана схема, поясняющая принцип действия n- разрядного сумматора с последовательным переносом. Число сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора младших разрядов установлен “0”, так как сигнал переноса сюда не поступает.

Рис. 1 Сумматор с последовательным переносом.

Рассмотрим синтез полусумматоров, имеющих два входа а и b. Выходными сигналами такого устройства являются сумма S и перенос Р, которые вырабатываются согласно таблице 1 функционирования данного устройства.

| a | b | S | P |

Таблица 1

Из таблицы следует, что полусумматор описывается двумя переключательными функциями:

S = not(a)*b + a*not(b), P = a*b (1) либо S = not(not(a)not(b) + a*b), P = a*b (2).

Его реализация на основании соотношений (1) либо (2) требует наличия, во-первых, логических элементов И, ИЛИ, НЕ, во-вторых, прямых a, b и инверсных а, b кодов слагаемых.

Воспользовавшись правилом инверсии, преобразуем (1) к виду, позволяющему построить полусумматор на логических элементах И-НЕ.

При синтезе комбинационных устройств (КУ) с несколькими выходами целесообразно логические функции преобразовать так, чтобы одно и то же логическое выражение в разных формулах использовалось несколько раз. Это позволит сократить общее количество логических элементов, необходимых для построения КУ.

В результате преобразования получим S = a*(not(P)) + b*(not(P)) P = a*b. Приведем их к виду, удобному для построения полусумматора только на элементах И-НЕ: S = not(not(a*not(P))not(b*not(p))) P=not(not(a*b)) (3).

Переключательные функции (3) реализуются на четырех двухвходовых схемах И-НЕ и одном инверторе.

Реализация полусумматора на элементах И-НЕ, И-ИЛИ-НЕ (а) и его условное обозначение(б)

Дата добавления: 2015-07-20; просмотров: 508 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Классификация счетчиков | | | Цифровые запоминающие устройства. Понятия, характеристики. |