T-триггер (от англ. toggle –кувыркаться) имеет один управляющий вход T. При появлении положительного (или отрицательного) фронта на входе T, состояние на выходе изменяется на противоположное.

Счетный триггер строится на основе JK-триггера путем объединения входов J и K. Как легко видеть из диаграммы состояний JK-триггера, в этом случае реализуются только 2 строки: J=K=0иJ=K=1.

Другой вариант построения T-триггера на основе динамического D-триггера.

4. Регистры. Последовательные и параллельные регистры. Схемы, принцип работы. Регистром цифровой узел, предназначенный для запоминания (хранения) двоичных чисел. Все регистры можно разделить на два основных типа: параллельные и последовательные

Параллельный регистр

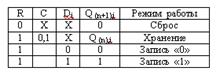

В простейшем случае параллельный регистр или регистр памяти представляет собой несколько (4 или 8) D-триггеров с общим входом синхронизации С.

Параллельные регистры могут строиться с использованием как статических, так и динамических триггеров. Регистры, построенные на триггерах-защелках, так и называются: «регистр-защелка».Кроме входа сброса R, регистры могут иметь вход разрешения записи Е, вход управления третьим состоянием выхода CS или OE. Различные ИМС регистров могут иметь различные комбинации перечисленных входов.

Последовательный регистр

Последовательный регистр

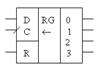

Последовательный или сдвиговый регистр (shift register) – это регистр, содержимое которого может сдвигаться в сторону младших или старших разрядов. В качестве примера рассмотрим 4-разрядный сдвиговый регистр, структурная схема и условное обозначение которого показаны на рис.14.

Из схемы видно, что выход каждого триггера соединяется со входом D последующего. Входной разряд данных подается на вход D 1-го триггера. В момент переднего фронта сигнала С состояние входа D записывается в 1-й триггер, состояние 1-го–во 2-й, 2-го–в 3-й и т. д. Т. о. каждый раз с приходом фронта синхросигнала С значение регистра сдвигается на 1 разряд влево. При этом в младший разряд записывается значение входа D, старший разряд теряется. Если на входе D лог. «0», то в каждом такте происходит умножение содержимого регистра на 2, за n тактов значение регистра умножается на 2n. Таблица истинности приведена в [3].Аналогично можно построить сдвиговый регистр для сдвига вправо. При этом за n тактов происходит деление на 2n.Существуют регистры, которые могут производить сдвиг как вправо, так и влево.В вычислительной технике распространенной является передача информации в последовательном коде. В этом случае сдвиговый регистр может использоваться для преобразования последовательного кода в параллельный.

5. Комбинационные узлы: дешифраторы и шифраторы. Схемы, принцип работы.

Дешифратор–это цифровой узел, преобразующий двоичный код на входе в унитарный код на выходе. Активный уровень имеется только на том выходе, номер которого соответствует входному коду (адресу). Полный дешифратор имеет n входов и2n выходов и называется n®2n. Каждый выход реализует один минтерм.

Дешифраторы часто используются для обращения к одному из нескольких устройств, адрес которого задается двоичным кодом. Обычно DC имеют также вход разрешения Е, часто называемом также «строб». При отсутствии разрешения все выходы неактивны.

Практически все DC на ИМС имеют инверсные выходы и один или несколько входов разрешения. Микросхемы обозначаются буквами ИД. Дешифратор с инверсными выходами и входом Е легко можно построить, модифицировав схему на рис. 32. Необходимо просто вместо ЛЭ «2И» использовать ЛЭ «3И-НЕ». На все третьи входы элементов И необходимо подать сигнал Е (если необходимо – с инверсией).

Неполный дешифратор.

Неполным дешифратором называется дешифратор, имеющий n входов и меньше, чем 2n выходов, т. е. реализующий не все минтермы.

Наибольшее распространение имеют двоично-десятичные дешифраторы «4 х 10», выпускаемые в виде ИМС. Шифратор выполняет преобразование, обратное DC. На вход CD подается унитарный код, а на выходе получается соответствующий ему двоичный код. Очевидно, что на входные сигналы накладывается ограничение (только одна единица), которое невыполнимо, если сигналы поступают от независимых источников, и не оговорено, как будет работать схема при поступлении произвольного кода. Поэтому схемы, подобные указанной, не выпускаются в виде ИМС и существуют чисто теоретически. Очевидно, что, если на вход поступает унитарный код, то схема работает как обычный шифратор, т.к. схема выделения старшей единицы не изменяет сигнал.

6. Последовательностные устройства: счетчики - назначение, классификация, основные определения. Двоичные счетчики.

Счетчиком называют устройство, сигналы, на входе которого в определенном коде отображают число импульсов, поступивших на счетный вход. Триггер Т-типа может служить примером простейшего счетчика. Такой счетчик считает до двух. Счетчик, образованный цепочкой из m-триггеров, сможет посчитать в двоичном коде 2m импульсов. Каждый из триггеров цепочки называют разрядом счетчика. Число m определяет количество разрядов двоичного числа, которое может быть записано в счетчик. Число Сч=2m называют коэффициентом (модулем) счета.

Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свое состояние, т. е. счетчик запоминает число сосчитанных импульсов.Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом.После каждого цикла счета на выходах последнего триггера возникают перепады напряжения. Это свойство определяет второе назначение счетчиков: деление числа входных импульсов.

У счетчиков в режиме деления используется только выходной сигнал последнего триггера. Такие делители имеют целочисленный коэффициент деления. Элементарная база современной микроэлектроники позволяет строить делители и с дробным коэффициентом деления.

На схемах счетчик обозначают буквами СТ (от counter – счетчик), иногда проставляют модуль СТ2.

Основные эксплуатационные показатели: емкость и быстродействие. Емкость равна коэффициенту счета – число импульсов, доступное счету за один цикл. Быстродействие определяется разрешающей способностью tразр.сч. Это минимальное время (min t) между двумя входными сигналами, в течение которого еще не возникают сбои в работе счетчика. Обратная величина fmax=1/tразр. сч. называется максимальной частотой счета. Время установки кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое состояние. Временные свойства зависят от временных характеристик триггеров и способа их соединения между собой.

Дата добавления: 2015-07-20; просмотров: 331 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| JK-триггер | | | Классификация счетчиков |