Читайте также:

|

Компаратор представляет собой комбинационное логическое устройство, предназначенное для сравнения двух чисел в цифровом коде. В данной схеме используется компаратор, реализующий функцию FA>B. Для одноразрядных слов функция FA>B определяется таблицей 4.1:

| A | B | FA>B |

Таблица 4.1– Таблица истинности для компаратора.

Из таблицы 4.1 видно, что

Функцию для FA>B для сравнения двухразрядных слов можно получить исходя из следующих условий. Если в старшем разряде слова А – единица, а слова В – нуль, то независимо от младших разрядов A>B и FA>B = 1. Если старшие разряды идентичны, то следует переходить к анализу младших, применив к ним то же условие, что и для старшего разряда. Функция FA>B при сравнении двухразрядных слов отображается картой Карно:

a1a0

b1b0

Выделение указанных в карте контуров приводит к формуле:

В базисе 3ИЛИ-НЕ эта функция будет иметь вид:

Для разработки данного восьмиразрядного компаратора в базисе 3ИЛИ-НЕ для достижения оптимальной характеристики быстродействие-простота сборки необходимо использовать компаратор групповой структуры, состоящий из четырех блоков сравнения для двухразрядных слов.

В нашем базисе двухразрядный компаратор имеет вид:

Рис 4.1– Схема и условное обозначение двухразрядного компаратора в базисе 3ИЛИ-НЕ

Восьмиразрядный компаратор можно построить в виде параллельно-параллельной структуры, выходной FA>B сигнал которой определен выражением:

FA>B=F3ÚF2ÚF1ÚF0

Тогда схема восьмиразрядного компаратора будет иметь

Рис 4.2– Схема и условное обозначение 8-разрядного компаратора

4.2 Составление комбинационной схемы  дешифратора.

дешифратора.

Дешифратор предназначен для управления мультиплексором в соответствии с алгоритмом Бута. Работает согласно таблице 4.2:

| A | B | C | X | Y | Z | Частичное произведение |

| A | ||||||

| A | ||||||

| 2A | ||||||

| -2A | ||||||

| -A | ||||||

| -A |

Таблица 4.2–таблица соответствия для дешифратора.

С помощью метода карт Карно находим соответствующие функции, которые после переводим в требуемый базис и составляем схему дешифратора.

Рис 4.3– Схема и условное обозначение дешифратора.

4.3. Составление комбинационной схемы сумматора.

4.3. Составление комбинационной схемы сумматора.

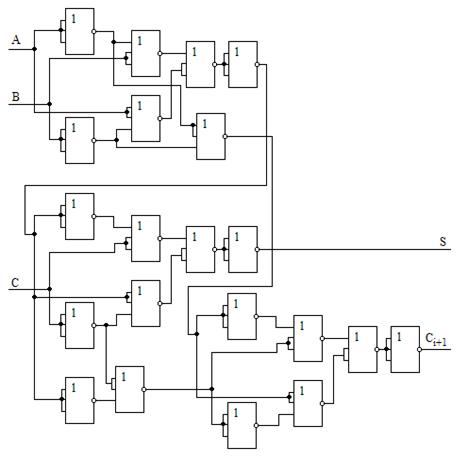

Для сложения двух 16-разрядных чисел используется 16-разрядный сумматор, включающий в себя 16 одноразрядных полных сумматоров, на входы которых подаются следующие данные: разряды двух слагаемых Аi и Bi, перенос с младшего разряда Ci (в частности для сложения нулевых разрядов всегда Ci=0 - вход заземлён).

На основе правил двоичной арифметики можно описать правила сложения двоичных цифр. При сложении двух чисел те разряды, в которых оба слагаемых равны единицы, можно рассматривать как источник переноса. Он поступает в соседний слева.

В тех разрядах, в которых оба слагаемых равны нулю, перенос ни при каких обстоятельствах образоваться не может, даже в том случае, если в этот разряд поступит перенос от соседнего справа разряда. Если в одном из слагаемых разряд равен 1, а во втором - 0 и был перенос в предыдущем разряде, то перенос будет и в данном разряде. Для полного одноразрядного сумматора можно составить следующую таблицу соответствия входных и выходных величин:

| Ai | Bi | Ci | Si | Ci+1 |

Таблица 4.3– Таблица соответствия для одноразрядного сумматора.

Большинство n -разрядных сумматоров состоит из n одноразрядных сумматоров, поэтому для дальнейшего рассмотрения остановимся на одноразрядном сумматоре.

Si = Ai  Bi

Bi  Ci

Ci

Ci+1 = Ai Bi  Ai Ci

Ai Ci  Bi Ci = Ai Bi

Bi Ci = Ai Bi  Ci (Ai

Ci (Ai  Bi)

Bi)

Рис 4.4– Схема и условное обозначение полного одноразрядного сумматора.

Для получения необходимого 16-разрядного сумматора нужно соединить 16 одноразрядных сумматоров так, чтобы выход переноса с младшего разряда соединялся с входом переноса старшего. Так как при умножении двух максимально-возможных восьмиразрядных чисел переполнение не возникнет, то необходимый нам сумматор может и не иметь выхода переноса.

Рис 4.5– Условное обозначение 16-разрядного сумматора.

Дата добавления: 2015-10-16; просмотров: 697 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| I. Описание алгоритма реализации операции. | | | Составление комбинационной схемы мультиплексора. |