Читайте также:

|

Каждая микросхема памяти организована как совокупность матриц элементов памяти, каждая из которых организована в виде строк и столбцов этих элементов. Запоминающие ячейки адресуются, т.е. приводятся в состояние готовности для операции записи или считывания из них информации, при совпадении сигналов возбуждения соответствующих строк и столбцов, которые поступают от дешифраторов старших и младших разрядов кода адреса.

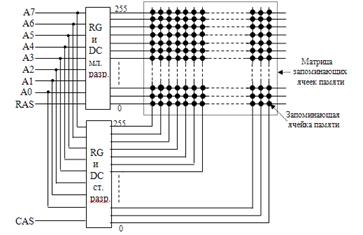

Упрощенная схема адресации запоминающих ячеек в микросхеме оперативной памяти объемом 64 кбит (принимая, что каждая запоминающая ячейка состоит из 1 запоминающего элемента, т.е. может хранить один бит информации), приведена на рис.VIII.1. Заданный 16 разрядный адрес поступает на микросхему в два приема: сначала 8 старших разрядов, которые по сигналу RAS (Row Address Strobe) записываются в регистр с дешифратором строк, а затем 8 младших разрядов, которые записываются по сигналу CAS (Column Address Strobe) в регистр с дешифратором столбцов. Сами операции считывания или записи осуществляются по переднему фронту тактового импульса системной шины (Clock) во время активного (низкого) уровня сигнала CAS. При этом чтение информации осуществляется при пассивном (высоком) уровне управляющего сигнала на входе записи микросхемы W (Write) или WE (Write Enable), а запись – при активном (низком) состоянии сигнала на этом входе.

Упрощенная схема адресации запоминающих ячеек в микросхеме оперативной памяти объемом 64 кбит (принимая, что каждая запоминающая ячейка состоит из 1 запоминающего элемента, т.е. может хранить один бит информации), приведена на рис.VIII.1. Заданный 16 разрядный адрес поступает на микросхему в два приема: сначала 8 старших разрядов, которые по сигналу RAS (Row Address Strobe) записываются в регистр с дешифратором строк, а затем 8 младших разрядов, которые записываются по сигналу CAS (Column Address Strobe) в регистр с дешифратором столбцов. Сами операции считывания или записи осуществляются по переднему фронту тактового импульса системной шины (Clock) во время активного (низкого) уровня сигнала CAS. При этом чтение информации осуществляется при пассивном (высоком) уровне управляющего сигнала на входе записи микросхемы W (Write) или WE (Write Enable), а запись – при активном (низком) состоянии сигнала на этом входе.

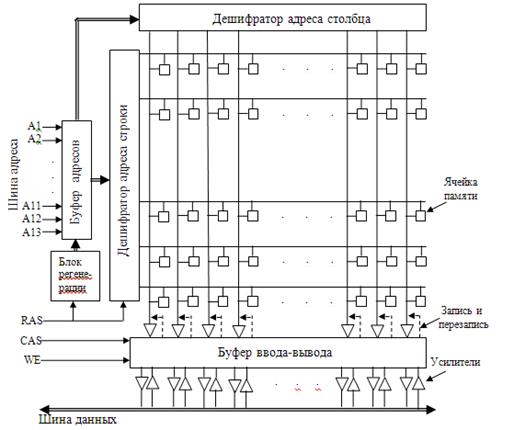

Более подробная схема отдельной матрицы памяти, с цепями ввода-вывода данных приведена на рис. VIII.2.

Заметим, что в современных микросхемах памяти, для задания адреса строки/столбца обычно используется 14-разрядная адресная шина, что позволяет адресовать 16 384 строки или столбца, но не более. Это ограничение по разрядности адресной шины затрудняет организацию микросхемы памяти емкостью 512 М бит в виде одной матрицы памяти. Этим и объясняется целесообразность использования нескольких матриц памяти в одной микросхеме, тем более, когда ширина шины данных микросхемы составляет 4,8,16, а в некоторых случаях и 32 бита.

Упрощенная структура запоминающего элемента SDRAM-памяти, которая предназначена для запоминания одного бита информации, приведена на рис. VIII.3. Она представляет собой конденсатор, который выполняет функцию хранителя заряда. Наличие заряда на конденсаторе определяет единичное значение бита информации, а его отсутствие – нулевое значение бита. Для возможности хранения заряда без его существенного уменьшения в течение определенного времени, конденсатор подключается к линии данных (линии столбца матрицы) через специальный транзисторный ключ. Этот ключ подключает конденсатор к внешней линии только в моменты записи или считывания с него информации или же в моменты регенерации его состояния.

При подаче на затвор транзистора отпирающего напряжения, поступающего по строке матрицы памяти (которые называют также адресными линиями), он подключается к линии столбцов. При этом заряд, хранящийся на конденсаторе данной ячейки, поступает в особый статический буфер, называемый усилителем уровня (Sense Amplifier), который установлен на выходе линии столбца, называемые также линиями данных.

При подаче на затвор транзистора отпирающего напряжения, поступающего по строке матрицы памяти (которые называют также адресными линиями), он подключается к линии столбцов. При этом заряд, хранящийся на конденсаторе данной ячейки, поступает в особый статический буфер, называемый усилителем уровня (Sense Amplifier), который установлен на выходе линии столбца, называемые также линиями данных.

Заметим, что при выборе строки открываются не один, а все транзисторные ключи, соединенные с этой линией строк, и данные окажутся на выходе усилителей по всем столбцам сразу. Это оказывается очень удобным при регенерации матрицы памяти. При операциях же считывания или записи информации, нужный элемент памяти выбирается подключением усилителя нужной линии данных в соответствии с кодом старших разрядов адреса, т.е. с кодом, подаваемым на дешифратор адреса столбца.

Кроме физической организации микросхемы памяти в виде нескольких параллельных матриц памяти, используется еще и логическое разделение микросхемы памяти на отдельные логические банки памяти (обычно на два или четыре логических банка, адресуемые сигналами по отдельным выводам BAi). Под банком памяти понимается набор совокупностей запоминающих матриц или набор отдельных микросхем, разрядность которого равна ширине шины памяти. (Отметим, что в информатике понятие банка определяет, вообще, совокупность совместно используемых однотипных элементов, средств или устройств).

Такое разделение памяти по банкам позволяет увеличить производительность за счет чередования банков памяти при обновлении состояния строк памяти. Дело в том, что, как это было упомянуто выше, каждые несколько миллисекунд элементы строк памяти динамического типа должны подвергаться регенерации, т.е. восстановлению своего состояния. Восстановление своего состояния элементы строк динамической памяти требуют и после каждой операции считывания. Логическое разбиение микросхемы памяти на несколько банков позволяет обращаться к строке одного логического банка, в то время пока строка другого банка обновляется. И, таким образом, в общем случае, может сниматься информация с одного банка данных, в то время как во втором осуществляется завершение переходных процессов установления адреса.

На рис.VIII.4 приведена упрощенная структура микросхемы памяти, в которой имеется четыре банка, каждый из которых состоит из восьми запоминающих матриц, содержащих по 8192 строки и 1024 столбца. Следовательно, емкость каждого банка составляет 8192×1024×8=213×210×23= =226=64 Мбит, т.е. полная емкость микросхемы составит 8 Мбайт. Вход CS (Chip Select) предназначен для подачи сигнала активирования (включения) данной микросхемы. Когда этот сигнал активен, возможен доступ к микросхеме памяти. В противном случае данная микросхема памяти недоступна.

На рис.VIII.4 приведена упрощенная структура микросхемы памяти, в которой имеется четыре банка, каждый из которых состоит из восьми запоминающих матриц, содержащих по 8192 строки и 1024 столбца. Следовательно, емкость каждого банка составляет 8192×1024×8=213×210×23= =226=64 Мбит, т.е. полная емкость микросхемы составит 8 Мбайт. Вход CS (Chip Select) предназначен для подачи сигнала активирования (включения) данной микросхемы. Когда этот сигнал активен, возможен доступ к микросхеме памяти. В противном случае данная микросхема памяти недоступна.

Для адресации запоминающих ячеек в таких микросхемах предусматривается дополнительные входы BA (Bank Address) - BA0 и BA1. Эти входы служат для ввода сигналов выбора необходимого банка памяти. Комбинации сигналов на этих входах: 00,01,10,11 позволяют задавать адреса четырех банков памяти.

Кроме того, поскольку в оперативной памяти современных компьютеров используются много микросхем, каждая микросхема имеет вход выбора (включения, активирования или инициирования) данной микросхемы – CS (Chip Select).

Сигнал на входе WE определяет режим записи (или считывания) микросхемы памяти. И, наконец, сигналы на входах CAS и RAS фиксируют в микросхеме адрес требуемой запоминающей ячейки памяти. Выводы D0…D7 служат для ввода байта информации при записи его в память, либо для вывода байта информации при его считывании из памяти.

Кроме емкости и количества банков каждая микросхема характеризуется шириной шины данных и глубиной микросхемы памяти.

Ширина шины данных определяется числом выводов (линий), предусмотренных для ввода (вывода) информации.

Эта величина соответствует разрядности данных при обмене информации с памятью при каждом обращении к ней. Ширина шины данных современных микросхем памяти обычно составляет 4,8,16 или 32 линии или разряда.

Глубиной микросхемы памяти называется число возможных адресов данной микросхемы, т.е. число возможных адресуемых совокупностей запоминающих элементов (запоминающих ячеек), хранящих коды, разрядность которых определяет ширину шины данных.

Эти параметры определяют логическую структуру микросхемы памяти. Например, память емкостью 1024 Мбит может быть организована как 128М×8, т.е. может быть микросхемой с глубиной 128М и шириной шины данных 8 бит. С другой стороны она может быть организована как 64М×16 или 32М×32, т.е. глубиной 64М или 32М и шириной шины данных, соответственно, 16 и 32 бит.

Для увеличения производительности подсистемы памяти используют и такой прием, как двухканальная или даже трехканальная организация памяти. В этом случае, каждый канал памяти использует свою отдельную шину (обычно 64-разрядную), через которую с помощью интегрированного контроллера памяти подключается к процессору.

Ранее упоминалось о том, что микросхемы памяти собираются на специальных платах в так называемые модули памяти, из которых уже формируются собственно оперативная память компьютера. Модули памяти и вся оперативная память компьютера, как и отдельные микросхемы, также характеризуется шириной шины данных и их глубиной, которая определяется как общая емкость, выраженная в битах, деленная на разрядность (ширину) шины данных. Заметим, что для всех современных оперативных запоминающих устройств персональных компьютеров ширина шины данных составляет 64 бита. В этом случае, оперативная память компьютера емкостью 512 Мбайт будет иметь глубину 64 М: (512×220×23) / 26 = 64×220 = 64М.

Микросхемы, размещенные на модулях SIMM, DIMM или RIMM, соединяются (группируются) в банки, для того чтобы модуль за одно обращение к нему процессора, выдавал в системную шину слова, соответствующей ширины (разрядности). Обычно она составляет 64, 128, 256 и 512 бит. В этом случае, банком памяти называют комплект микросхем, обеспечивающий для данной системы требуемую разрядность хранимых данных, выбираемых за одно обращение к памяти.

Одной из главных характеристик основной оперативной памяти является ее пропускная способность.

Пропускной способностью оперативной памяти называется максимальное количество данных, которое можно записать в память либо считать из нее в единицу времени.

Она зависит от ширины шины данных и максимально возможной частоты обращения к памяти. Ширина шины данных определяет количество бит информации, передаваемых за один такт, а частота обращения – количество тактов в единицу времени. Поэтому, чтобы определить пропускную способность памяти надо умножить частоту системной шины на ширину шины данных. Поскольку современные оперативные запоминающие устройства персональных компьютеров имеют ширину шины данных равную 64 бит (8 байт), то, например память, функционирующая на частоте системной шины равной 800 МГц, имеет пропускную способность 6,4 Гбайт/с (800 МГц × 8 байт).

Кроме максимальной пропускной способности, память характеризуется так называемой латентностью. Под латентностью понимается задержка между поступлением команды и моментом ее реализации. Латентность памяти определяется ее таймингами, т.е. задержками, измеряемыми в количестве тактов, между отдельными командами. Принято различать несколько разновидностей таймингов памяти, соответствующих задержкам между различными командами. Рассмотрим их подробнее.

Дата добавления: 2015-10-26; просмотров: 221 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| РАЗМЕЩЕНИЕ ЗУ НА СИСТЕМНОЙ ПЛАТЕ (НЕТУ) | | | СПОСОБЫ АДРЕСАЦИИ ИНФОРМАЦИИ В КОМПЬЮТЕРЕ |