|

Читайте также: |

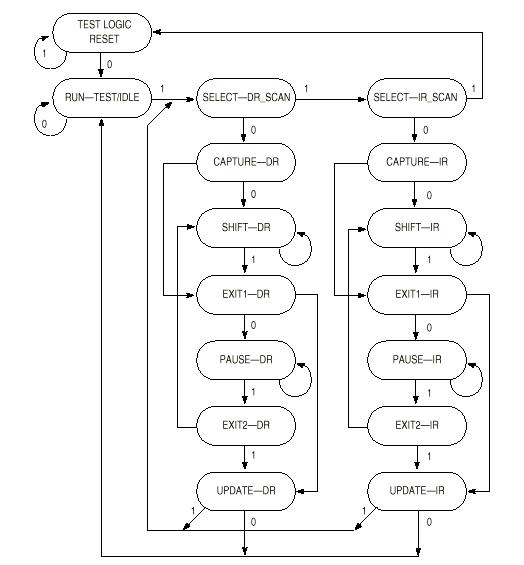

ТАР – контроллер отвечает за интерпретацию логических значений сигнала TMS. Он является синхронным цифровым автоматом, контролирующим JTAG – логику. Значения, указанные на графе рядом с состояниями (помечены овалами), отражают значение сигнала TMS, стробируемое положительным фронтом сигнала ТСК (см. рис. 4).

Рис. 4. Граф состояний ТАР – контроллера

Как видно из графа, TAP-контроллер перейдет в исходное состояние RESET из любого другого не более чем за 5 импульсов TCK при TMS=1. При этом произойдет сброс всей схемы BST, а в регистр инструкций запишется значение по умолчанию (как правило, инструкция IDCODE, но может и другая, например, SAMPLE. Во избежание этого сброса следует проводить контроллер TAP через безопасное состояние IDLE, в котором все рабочие установки сохраняются.

Схема ВST содержит целый набор сдвиговых регистров. При проходе по правой ветви графа доступен регистр инструкций длиной от 3 бит. Загруженная инструкция определяет один из регистров данных, доступных при проходе по левой ветви и действия с ними в определенных состояниях TAP-контроллера. Из этих регистров, как минимум, в наличии обычно имеются регистр доступа к внешним выводам чипа и однобитный регистр обхода.

Поскольку в цепочке JTAG-устройств все сдвиговые регистры складываются в один длинный, то регистр обхода позволяет уменьшить эту длину, представляя обойденные устройства всего одним битом. Для этого служит инструкция BYPASS. Поскольку ввод инструкции BYPASS отменяет действие ранее загруженной инструкции, к сожалению, невозможно сохранить состояние блоков ввода-вывода, устанавливаемое инструкциями типа EXTEST и INTEST. Исключением является инструкция CLAMP, после которой можно использовать регистр обхода. Но эта инструкция практически не встречается.

В регистре доступа для каждого блока ввода-вывода ПЛИС, как правило, отведены три последовательных бита: вход (I), выход (O) и запрет выхода (T). Порядок вывода бит на TDO различен для ПЛИС разных фирм. Например, для Xilinx - (T,O,I), а для Altera - (I,T,O).

В состоянии CAPTURE в выбранный сдвиговый регистр записывается текущее состояние. Кстати, для регистра инструкций обычно это код инструкции SAMPLE, а для регистра обхода - логическая единица. В состоянии UPDATE данные из сдвигового регистра переписываются в соответствующий регистр хранения.

Таким образом инструкция SAMPLE не только считывает текущее состояние внешних выводов, но и записывает в регистре хранения управляющие данные. Поэтому, чтобы избежать вывода случайной информации, ее используют перед загрузкой инструкций типа EXTEST или INTEST.

При загрузке инструкции EXTEST выходы регистра хранения определяют состояние выходов чипа, т.е. управляют выходом и его третьим состоянием. Таким образом можно протестировать внешние межсоединения. Инструкция INTEST, напротив, подменяет сигнал вводимый внутрь чипа и служит для проверки самого чипа. Часто обходятся одной инструкцией EXTEST, используя бит входа (I) для ввода в чип как в инструкции INTEST.

Инструкция IDCODE подключает встроенный 32-битный регистр с идентификаторами производителя, модели и версии устройства. Формат регистра представлен в табл. 2.

Таблица 2.

| Version | Part Number | Manufacturer Identity | Fixed "1" |

| Биты 31-28 | Биты 27-12 | Биты 11-1 | Бит 0 |

Выводы

Итак, стандарт IEEE 1149.1, известный как Test Access Port and Boundary Scan Architecture, явил собой новое слово в технике тестирования и контроля высокотехнологичных современных полупроводниковых устройств. Он воплотил в себя теоретические разработки группы компаний и отдельных инженеров, организовавших специальную организацию JTAG. В самых общих словах, стандарт устанавливает следующие положения:

1. Любое полупроводниковое устройство, совместимое с JTAG, включает в себя, помимо основной логики, специальные Boundary Scan соты, которые в нормальном режиме не влияют на работу схемы, а в активном – являются генераторами и приемниками тестовых сигналов.

2. По возможности, каждый логический вывод микросхемы должен иметь свою Boundary Scan соту.

3. Boundary Scan соты управляются ТАР – контроллером, имеющим всего четыре ножки управления, а опционально – пять.

4. ТАР – контроллер имеет стандартный минимум команд, поступающих на его входы в последовательном коде от персональной ЭВМ либо другого устройства, позволяющий организовать различные режимы работы Boundary Scan соты.

Таким образом, для устройств, собранных на элементах, отвечающих рекомендациям стандарта IEEE 1149.1, значительно упрощаются процедуры, связанные с тестированием, контролем и диагностикой. Не требуется разрушать связи на печатной плате, подключать внешние схемы контроля (тестеры, осциллографы и т.д.). Достаточно лишь через специальный разъем подключить ЭВМ и, воспользовавшись готовой или самостоятельно написанной программой, снимать и устанавливать любые логические значения и режимы работы микросхем в проверяемом устройстве. В результате диагностики, к примеру, можно получить данные не только о том, какой элемент неисправен, но и какой его логический выход (либо цепь, являющаяся для него нагрузкой).

Дата добавления: 2015-09-02; просмотров: 86 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Простой тест на уровне платы | | | Управление сетью |