Читайте также:

|

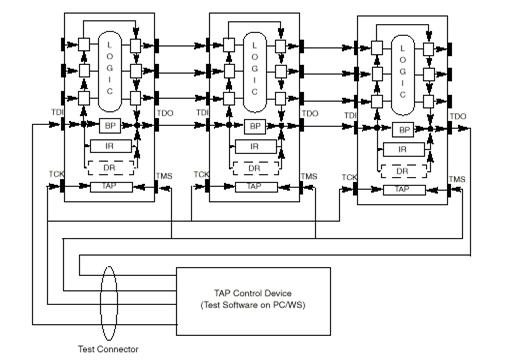

Одним из первых тестов, проводимых для печатной платы, должен являться так называемый тест инфраструктуры. Этот тест используется для того, чтобы установить, все ли компоненты смонтированы правильно. При этом тесте два последних бита регистра инструкций (IR) всегда равны «01». «Выдвигая» содержимое IR каждого устройства в цепочке, можно различить, правильно ли установлена микросхема. Это достигается последовательным чтением

|

Рис. 3 Одиночная Boundary Scan цепочка на плате.

IR регистра посредством ТАР – контроллера.

После успешного завершения предыдущего теста, начинается тес проверки соединений компонентов. Ищутся обрывы или замыкания. Тестовые последовательности предустанавливаются на выводы, работающие на выход. Используется команда EXTEST. Эти последовательности попадают на входы следующих элементов и сдвигаются в последовательном коде на TDO для последующего анализа.

Тестовые образцы генерируются и анализируются программным образом. Пример программ подобного типа - Automatic Test Pattern Generation (ATPG) или Boundary scan Test Pattern Generation (BTPG).

Дата добавления: 2015-09-02; просмотров: 35 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Обязательные инструкции | | | Граф состояний ТАР – контроллера |