|

Читайте также: |

Архитектура Boundary Scan позволяет проводить полное тестирование и обзор компонентов, совместимых со спецификацией JTAG, без использования специальных устройств, подключаемых к плате. Контроль и диагностика осуществляются программным путем, так как каждое устройство (микросхема) снабжены собственными схемами тестирования, выдающими результат внутренней проверки через стандартные шины.

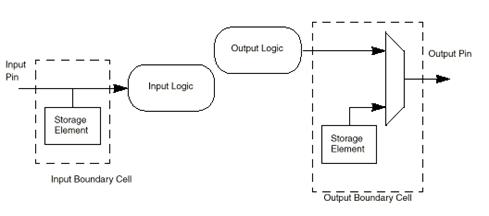

Рис. 1 Входные и выходные структуры для Boundary Scan устройств.

На рис.1 изображена возможная структура для входных и выходных ножек JTAG – совместимых устройств. Во время стандартных операций boundary – соты не активны и данные проходят обычным образом через элемент. Во время режима тестирования все входные сигналы сохраняются для анализа, а все выходные сигналы устанавливаются таким образом, чтобы организовать процесс тестирования для последующих устройств. Функционирование таких сканирующих сот контролируется через Test Acsess Port (TAP) контроллер с использованием регистра инструкций, как показано на рис.2.

Рис. 2. Устройство (микросхема), поддерживающая Boundary Scan.

Рис. 2. Устройство (микросхема), поддерживающая Boundary Scan.

ТАР – контроллер – это устройство (может находиться в одном из 16 состояний), контролирующее операции связанных архитектурой Boundary Scan сот. Основные операции контролируются через четыре вывода: Test Clock (TCK) – частота синхронизации теста, Test Mode Select (TMS) – выбор режима тестирования, Test Data In (TDI) – вход тестовых данных, и Test Data Out (TDO) – выход тестовых данных.

Входы TCK и TMS определяют переходы ТАР – контроллера в различные состояния. Выводы TDI и TDO определяют тестовые данные для сканируемой цепочки. Еще может использоваться пятый вывод, TRST, для асинхронного сброса ТАР – контроллера.

Дата добавления: 2015-09-02; просмотров: 55 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Основы JTAG Boundary Scan архитектуры | | | Обязательные инструкции |