Регистр — это операционный узел цифровых устройств для запоминания слов и для выполнения над словом некоторых логических преобразований. Регистр — это совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных комбинационных схем для выполнения операций:

установки регистра в 0 («сброс»);

приема слова из другого регистра, сумматора;

передачи слова в другой регистр;

сдвига слова вправо или влево на требуемое число разрядов;

преобразования последовательного кода слова в параллельный и наоборот;

поразрядных логических операций.

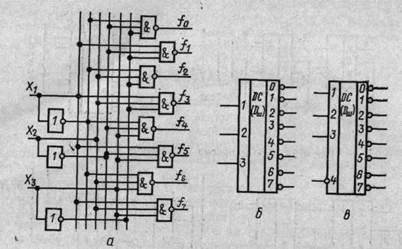

На рис. 6.16, а, б показана схема приема информации в регистр. Для этого используется парафазная передача информации, при которой на одном из входов триггера обязательно присутствует сигнал 1, устанавливающий триггер в нужное состояние независимо от той информации, которая в нем хранилась.

Как правило, операция передачи кода с регистра объединяется с операцией приема этого кода в другой регистр. Это показано на рис. 6.17, где информация передается из регистра РГ1 в регистр РГ2 парафазным кодом под действием сигнала ПРРГ2, управляющего приемом информации в регистр.

Операция сдвига кода — это перемещение в регистре всех разрядов кода слова на одинаковое число разрядов влево или вправо. В этом случае разряды слова, вышедшие из разрядной сетки регистра влево (или вправо), теряются, а в освободившиеся при сдвиге разряды регистра записываются нули.

Функциональная схема сдвигающего регистра на RS -триггерах приведена на рис. 6.18.

Сигналом Cдb(τ1) код в регистре передается со сдвигом с выходных (основных) триггеров на входные (дополнительные) триггеры соседних разрядов, а потом сигналом С дв (τ2) переписывается с входных триггеров на выходные триггеры в тех же самых разрядах. Сигналы С дв ( τ1 ) и С дв (τ2) во времени не совпадают. Несколько регистров общего назначения (ΡΟΗ) образуют сверхоперативное запоминающее устройство (СОЗУ).

Имеется большая номенклатура ИС, позволяющая реализовать требуемую структуру регистра. В ряде комплектов микропроцессорных наборов имеется многофункциональный буферный

Рис. 6.16. Схемы приема информации в регистр

Рис. 6.17. Схема передачи информации из одного регистра в другой Рис. 6.18. Сдвигающий регистр на RS -триггерах

Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в сигнал на одном из выходов.

Если на входы дешифратора подаются двоичные переменные, то на одном из выходов дешифратора вырабатывается сигнал 1, а на остальных выходах сохраняются сигналы 0. Дешифратор как операционный узел выполняет микрооперацию

Рис. 6.19. Дешифратор с инверсными входами

Рис. 6.20. Каскадный дешифратор Рис. 6.21. Схема шифратора клавиатуры

преобразования позиционного двоичного хода в унитарный цифровой код.

В общем случае дешифратор с n входами имеет 2 n выходов (рис. 6.19, а, б, в), так как n -разрядный код входного слова может принимать 2 n различных значений и каждому из этих значений соответствует сигнал 1 на одном из выходов дешифратора.

На выходах дешифратора с номерами 0, 1, 2,..., 2п-1 вырабатываются значения булевых функций соответственно:

f 0 = ХпХп-1 · · · Х2Х1; f1 = ХпХп-1 · · · Х2Х1;

f2 = ХпХп-1 · · · Х2Х1;

· · · · · · · · · · · ·

f2n-1 = ХпХп-1 · · · Х2Х1; (6.7)

Дешифраторы часто устанавливаются в цифровых схемах на выходах регистров или счетчиков и служат для преобразования кода слова, находящегося в регистре (в счетчике), в управляющий сигнал на одном из выходов дешифратора.

На рис. 6.19, α показан способ построения дешифратора на примере схемы дешифратора с инверсными выходами для трехразрядного входного слова. Схема представляет собой набор из восьми трехвходных элементов И — НЕ, на входы которых поданы все возможные комбинации прямых и инверсных значений разрядов слова.

Если каждый выходной элемент дешифратора имеет вход для сигнала синхронизации, то такая схема называется дешифратором со входом синхронизации (рис. 6.19, в). При С=0 он будет работать так же, как схема на рис. 6.19, б. Такого вида схемы выпускаются в составе комплексов интегральных логических элементов.

Из логических элементов, являющихся дешифраторами, можно строить дешифраторы на большое число входов. При этом, как правило, используются дешифраторы с инверсными выходами и инверсными входами синхронизации.

Каскадное включение таких схем позволяет легко наращивать число дешифрируемых переменных.

Принцип построения таких схем показан на рис. 6.20. Здесь дешифратор на 4 входа с инверсными выходами, построенный из интегральных элементов, реализующих схемы двухвходовых дешифраторов.

Шифратор — комбинационная схема для преобразования унитарного (однопозиционного) кода в двоичный позиционный. Типичным примером является шифратор клавиатуры для ввода

в цифровое устройство шестнадцатиричного кода (рис. 6.21). При ненажатых клавишах на всех входах шифратора обеспечивается 0, а нажатая клавиша подает на соответствующий вход шифратора 1. Шифратор вырабатывает также осведомительный сигнал Ζ при нажатии любой из клавиш. Уравнения, описывающие структуру шифратора, имеют следующий вид:

y1= 1+3 + 5 + 7 + 9 + B + D + F;

y 2 = 2 + 3 + 6 + 7+ A+B+E +F;

y 4 = 4 + 5 + 6 + 7 + С+D +E+F;

y 8 = 8 + 9 + A+B + C + D+E + F;

Z = 0+1+2=3+4+5+6+7 + 8 + 9 + A +B+C+D +E + F.

(6.8) 6.7. СЧЕТЧИКИ, СУММАТОРЫ

Счетчик — операционный узел цифрового устройства, обеспечивающий хранение слова информации и выполнение над ним микрооперации счета.

Микрооперация счета состоит в изменении значения слова или состояния счетчика на 1.

Счетчик, на котором реализуется микрооперация счета вида С: = С+1, называется суммирующим.

Если на счетчике реализуется микрооперация С: = С —1, то такой счетчик называется вычитающим. Счетчик, на котором реализуются обе эти микрооперации, называется реверсивным.

Счетчики применяются для подсчета шагов программы, циклов сложения, вычитания, умножения, деления, преобразования кодов, построения распределителей импульсов, накапливающих сумматоров, пересчетных устройств и т. д. Пересчетное устройство— это цифровой операционный узел, обеспечивающий хранение слова информации и выполнение над ним микрооперации

Таблица 6.5

произвольной смены состояния, благодаря чему определения «суммирующий», «вычитающий», «реверсивный» неприменимы к пересчетным устройствам.

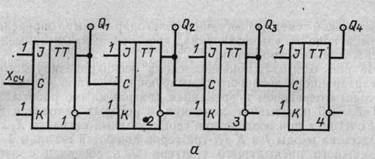

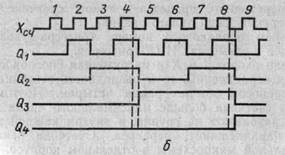

На рис. 6.22, а, б показана схема несинхронизируемого четырехразрядного двоичного суммирующего счетчика с последовательным переносом и временная диаграмма его работы.

Табл. 6.5 показывает состояния, в которых находятся триггеры счетчика при воздействии серии входных сигналов Х СЧ.

Здесь на входы I и К IK -триггеров подаются сигналы 1. Выход каждого предыдущего триггера Q n-1 соединен с входом синхронизации Сп последующего триггера.

Каждый IK -триггер в счетчике выполняет функцию несинхронизируемого триггера со счетным входом. По спаду единичного выходного сигнала изменяется состояние триггера младшего разряда счетчика на противоположное (т. е. реализуется сложение по модулю 2 в этом разряде). В последующих разрядах аналогичное действие производит сигнал переноса.

Обычно счетчик имеет цепь установки в нулевое состояние (сброс триггеров в 0). Однако начальное состояние счетчика необязательно нулевое. Начальное состояние может устанавливаться передачей в счетчик кода некоторого числа, и с него будет начинаться операция счета единиц.

Такой режим работы счетчика необходим, например, при образовании последовательности адресов команд при заданном исходном адресе.

С ростом разрядности n счетчика снижается предельная частота его работы, так как возрастает задержка поступления сигнала на вход С некоторого j -го разряда относительно времени поступления входного сигнала Х сч на входе С младшего разряда счетчика.

Из временной диаграммы видно, что такая задержка может привести к искажению информации в счетчике (моменты времени 4 и 8).

Для повышения быстродействия счетчики выполняют с параллельным переносом (рис. 6.23, а, б). Выходы всех предшествующих разрядов подаются на входы I и К j -го триггера. Длительность переходного процесса в таком счетчике равна длительности переключения одного разряда.

С возрастанием порядкового номера триггера увеличивается число входов в элементах И IK -триггеров.

Так как число входов I и К и нагрузочная способность выходов триггеров ограниченны, то и разрядность счетчика с параллельным переносом обычно равна четырем. Поэтому при числе разрядов счетчика больше максимального числа входов I и К счетчик разбивают на группы и внутри каждой группы строят цепи параллельного переноса. Счетчики реализуют в виде интегральной микросхемы в отдельном корпусе.

В этом случае при последовательном переносе просто осуществляется увеличение разрядности счетчика.

Вычитающие счетчики и реверсивные (настраиваемые на суммирование и вычитание) строятся аналогичным образом.

Сумматоры. Это узлы ЭВМ, выполняющие арифметическое суммирование кодов чисел. Сумматор—это комбинация одноразрядных суммирующих схем. При сложении двух чисел в каждом разряде производится сложение трех цифр: цифры данного разряда первого слагаемого, цифры данного разряда второго слагаемого и цифры (1 или 0) переноса из соседнего младшего разряда.

В результате сложения для каждого разряда получается цифра суммы для этого разряда и цифра (1 или 0) переноса в следующий старший разряд.

Пример сложения двоичных чисел приведен в табл. 6.6.

Таблица 6.6

| Цифры переноса из предыдущего разряда pi | Первое слагаемое ai | Второе слагаемое bi | Сумма si | Цифра переноса в старый разряд Pi+1 |

По табл. 6.6 составим булевы функции для описания одноразрядного сумматора-устройства, вырабатывающего на выходе сигналы суммы и переноса при поступлении на входы двух цифр слагаемых и цифры переноса из предыдущего младшего

разряда:

s i = aibipi V aibipi V aibipi V aibipi (6.9)

pi+1 = aibipi V aibipi V aibipi V aibipi, (6.10)

где pi — цифра переноса из предыдущего младшего разряда; ai, bi — цифры слагаемых в данном разряде; s i — сумма; Pi+1 — цифра переноса в старший разряд.

Рис. 6.22. Несинхронизируемый двоичный счетчик с последовательным переносом

Рис. 6.23. Синхронизируемый двоичный счетчик с параллельным переносом

Выражение для цифры переноса в следующий разряд может быть приведено к более простому виду:

pi+1 = aibi V aipi V bipi. (6.11)

Преобразуя с помощью правил булевой алгебры выражения для цифры суммы и цифры переноса, можно получить различные соотношения, которым будут соответствовать варианты построения схем полных сумматоров. Параллельный многоразрядный сумматор может быть составлен из одноразрядных сумматоров, число которых равно числу разрядов слагаемых,

Рис. 6.24. Параллельный сумматор с последовательным переносом

путем соединения выхода, на котором формируется сигнал переноса соседнего старшего разряда (рис. 6.24).

После того, как выработан результат сложения на выходах комбинационных схем формирования суммы, он обычно запоминается в отдельном триггерном регистре.

Сумматоры с поразрядным последовательным переносом. Как показано на рис. 6.24, перенос распространяется последовательно от разряда к разряду по мере образования цифры суммы в каждом отдельном разряде. При наиболее неблагоприятных условиях для распространения переноса, например при сложении чисел 11... 11 и 00...001, произойдет «пробег» 1 переноса через весь сумматор от самого младшего разряда к самому старшему. Поэтому в худшем случае время распространения переноса

T пер = τ1 n, (6.12)

где τ1— время распространения переноса в одном разряде; n — число разрядов сумматора.

Сумматоры с параллельным переносом. Сложение выполняется как поразрядная операция и на распространение переноса не требуется дополнительного времени. Этот прин-

цип используется в сумматорах с групповым переносом. Сумматор разбивается на несколько групп примерно равной длины. Сигнал переноса, поступающий на вход младшего разряда группы, при наличии условий распространения переноса во всех разрядах данной группы, передается на вход младшего разряда соседней, более старшей группы в обход данной

группы.

Сумматор является одним из основных узлов арифметического устройства. Широко используются сумматоры в виде ИС К155ИМ1, К155ИМ2, К155ИМЗ и др.

Дата добавления: 2015-08-27; просмотров: 847 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| ТРИГГЕРЫ | | | АРИФМЕТИЧЕСКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО (АЛУ) |