Основные характеристики. Это элементы, которые по выходным сигналам могут находиться в одном из двух устойчивых состояний: 1 и 0.

Под влиянием входного сигнала триггер скачкообразно переходит из одного устойчивого состояния в другое, скачкообразно меняя уровень напряжения выходного сигнала.

В цифровой автоматике используются триггеры с двумя выходами: прямой Q — выход 1, инверсный Q — выход 0.

В единичном состоянии триггера на выходе Q — высокий уровень сигнала, а в нулевом — низкий. На выходе Q — наоборот.

В ИС элементов триггер и схема, управляющая его входами (входная логика), выполняются на одной кремниевой пластине, заключенной в корпус с выводами. В одном корпусе может быть несколько триггеров.

Триггеры делятся на несколько типов: с установочными входами RS -триггер; со счетным входом T -триггер; D — триггер; IK -триггер и др.

Если хотя бы с одного входа информация в триггер заносится принудительно синхронизирующим сигналом, то триггер называется синхронизируемым (синхронным).

Если занесение информации в триггер с любого входа производится без синхронизирующего сигнала, это несинхронизи-руемый (асинхронный триггер).

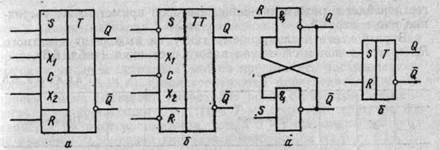

Общая форма условного обозначения триггеров показана на рис. 6.9.

В основном поле ставится символ Τ или ТТ для обозначения однотактного или двухтактного триггера.

Дополнительное поле может делиться на 2 части: асинхронную и синхронную. В первой проставляются символы R и S входов несинхронизируемой установки триггера в 1 и 0, во второй — на местах Х1 и Х2 символы в соответствии с типом триггера. При этом пользуются обозначениями для входов: S — вход установки триггера в 1; R — вход установки триггера в 0; T — вход триггера со счетным входом; D — вход D -триггера; I — вход для синхронизируемой установки состояния 1 в IK -триггере; К — вход для синхронизируемой установки состояния 0 в IK -триггере; С — вход синхронизации.

Если вход отмечен кружком, это значит, что действующее значение входного сигнала — 0. На рис. 6.9, а отсутствие кружка на входе С — действующее значение синхронизирующего сигнала равно 1, на рис. 6.9, б действующее значение синхронизирующего сигнала 0.

Состояние триггера определяется сигналом Q на прямом выходе или сигналом Q на его инверсном выходе.

Законы функционирования триггеров задаются таблицами переходов с компактной записью, причем в столбце состояний может быть указано, что новое состояние совпадает с предыдущим, либо является его отрицанием.

Асинхронный RS -триггер на интегральных элементах ИЛИ — НЕ показан на рис. 6.10. Триггер образован из двух комбинированных схем ИЛИ — НЕ, соединенных таким образом, что возникают положительные обратные связи, благодаря которым в устойчивом состоянии выходной транзистор одной схемы ИЛИ — НЕ закрыт, а другой открыт.

Таблица переходов определяет закон функционирования триггера (табл. 6.1).

Таблица 6.1

| R | S | Q | Примечание | R | S | Q | Примечание |

| 0 0 | 0 1 | Q | Хранение Установка 1 | 1 1 | 0 1 | - | Установка 0 Запрещено |

Функционирование RS -триггера можно описать выражением Q(t+1) = S(t)VQ(t)R(t), (6.4)

где S(t)R(t) = 0; t — момент времени, предшествующий смене состояния.

Синхронизируемый однотактный RS -триггер на элементах

И — НЕ. На рис. 6.11элементы 1 и 2 образуют схему входной логики асинхронного RS -триггера, построенного на элементах 3 и 4. Такие RS -триггеры имеют два информационных входа R и S и вход синхронизации С.

Кроме того, триггер может иметь несинхронизируемые входы R и S. В этом случае функционирование триггера осуществляется либо под воздействием несинхронизируемых входов при С =0, либо под воздействием синхронизируемых входов. В последнем случае на несинхронизируемых входах должны присутствовать сигналы, которые не влияют на состояние схемы.

Таблица 6.2

| R | S | Q | Примечание | R | S | Q | Примечание |

| 1 1 | 1 0 | Q 1 | Хранение Установка 1 | 0 0 | 1 0 | - | Установка 0 Запрещено |

Табл. 6.2 определяет переходы RS -триггера для синхронизируемых входов R и S.

Работа в соответствии с табл. 6.2 осуществляется при сигнале несинхронизируемого входа R=1 и при С=1.

Входная информация в парафазном коде заносится в синхронизируемый RS -триггер через элементы входной логики 1 и 2 в момент поступления сигнала синхронизации С. В отсутствие сигнала синхронизации триггер может быть установлен в состояние 0 путем подачи на несинхронизируемый вход R сигнала R =0.

Двухтактный RS -триггер. Устойчивая работа однотактных RS -триггеров в схеме с передачей информации между триггерами возможна только в случае, если занесение в триггер информации осуществляется после завершения ее передачи о прежнем его состоянии в другой триггер. Это обеспечивается при использовании двух серий находящихся в противофазе синхросигналов. На этом и построены двухтактные RS -триггеры.

На рис. 6.12 схема двухвходового двухтактного RS -триггер а. Она состоит из двух однотактных RS -триггеров и инвертора в цепи синхронизации.

При поступлении на вход RS -триггера сигнала С= 1 входная информация заносится в первый однотактный RS -триггер, а второй при этом будет хранить информацию, относящуюся к, предыдущему периоду представления. По окончании действия сигнала синхронизации, когда С =0, а С =1, первый RS -триг-

Рис. 6.9. Схема условного обозначения триггеров

Рис. 6.10. Асинхронный RS -триггер на интегральных элементах ИЛИ —НЕ: а — функциональная схема; б — общий вид

Рис. 6.11. Синхронизируемый однотактный RS -триггер на элементах И—НЕ: а — функциональная схема; б — общий вид

Рис. 6.12. Двухвходовой двухтактный RS -триггер на элементах И—НЕ

гер перейдет в режим хранения, а второй примет то же состояние, что и первый.

В результате к следующему такту на выходе двухтактного RS -триггера появится сигнал нового состояния (табл. 6.3).

Таблица 6.3

| t | t+1 | Примечание | t | t+1 | Примечание | ||

| R | s | Q | R | S | Q | ||

| 0 1 | 0 0 | Q 0 | Хранение Установка 0 | 0 1 | - | Установка 1 Запрещено |

Такты t здесь задаются интервалами времени, в которые С=1. Двухтактный триггер изменяет свои состояния только после окончания действия сигнала синхронизации С= 1 (переход в режим хранения информации).

Поэтому из двухтактных триггеров можно строить произвольные схемы; в том числе подавать сигналы с выхода триггера на его вход.

Для установки триггера в состояние 0 или 1 без использования синхросигналов в схему вводят дополнительные входы R и S несинхронизируемой установки. Связи с этими входами показаны пунктирами. При подаче 0 на вход R(S) и 1 на вход S(R) оба однотактных триггера устанавливаются в состояние 0(1). При подаче 1 на оба этих входа работа триггера осуществляется в соответствии с таблицей.

RS -триггеры составляют основу для построения других триг-герных схем: Т, D, IK -триггеров.

Т-триггер (рис. 6.13). Триггер со счетным входом (T -триг-гер) в простейшем случае может быть построен с использованием двухтактного синхронизируемого RS -триггера. T -триггер должен реализовать функцию вида

Q(t + l) = Q(f)T(t)VQ(t)T(t). (6.5)

На рис. 6.13, α поступление сигнала Т=1 приводит к записи в двухступенчатый RS -триггер состояния, противоположного ранее хранимому. При этом, так как триггер двухступенчатый, на его выходе сигнал изменится только по завершению действия сигнала Т=1, что исключает возникновение генерации в схеме с обратной связью. В этой схеме 6.13, α единичный входной сигнал представляется спадом сигнала T =1, так как при любой продолжительности сигнала Т=1 изменение состояния T -триг-гера происходит только один раз — при снятии сигнала Т= 1 (рис. 6.13, б).

При необходимости представить потенциалом последовательность единиц на входе T -триггера используется синхронизируемая схема (рис. 6.13, в, г). Здесь единичный входной сигнал представляется высоким уровнем сигнала Τ при С =1. Поэтому высоким уровнем сигнала Τ можно представить последовательность 1 (рис. 6.13, д). Запись в триггер происходит при С =1, причем смена состояния происходит после окончания действия сигнала синхронизации С =1. При Т= 1 состояние триггера изменяется на противоположное, а при T = 0 состояние триггера не меняется (временная диаграмма изображена на рис. 6.13,(д).

Рис. 6.13. T-триггер

D -триггер (рис. 6.14). Это широко распространенный интегральный D -триггер, который реализует функцию временной задержки. D -триггер имеет только режимы установки 1 и 0. Поэтому несинхронизируемый D -триггер (рис. 6.14, а) не применяется, так как его выход будет просто повторять входной сигнал. Синхронизируемый однотактный D -триггер (рис. 6.14, б) задерживает распространение входного сигнала на время паузы между синхросигналами (задержка на полпериода). Для задержки на период (на один такт) используется двухтактный D -триггер (рис. 6.14,в). Под действием синхросигнала С поступающая на вход D информация принимается в RS- триггер, но на выходе Q появляется с задержкой на такт

Q(t +1) = D(t).

Выпускаются D -триггеры К155ТМ2 и др.

IK-триггер (двухтактный). Распространен в системах интегральных логических элементов (рис. 6.15, а, б, в). Имеются входы несинхронизируемой установки R и S, при помощи которых при С=0 триггер может быть установлен в состояние 1 путем подачи R=1 и S =0, либо в состояние 0 путем подачи R=0 и S =1. При подаче сигналов R = S=1, не меняющих состояние схемы, работа триггера осуществляется под воздействием синхронизируемых входов. В этом случае работа IK -триггера описана в табл. 6.4, причем такты t здесь, как и ранее, задаются сигналом С= 1.

Таблица 6.4

| t | t+1 | Примечание | t | t+1 | Примечание | ||

| I | к | Q | I | К | Q | ||

| 0 0 | 0 1 | Q 0 | Хранение Установка 0 | 0 1 | Q | Установка 1 Инверсия |

Здесь I=I1I2I3 и К = К1К2К3. Входы I и К соответствуют входам установки в 1 и в 0 триггера. Однако в отличие от RS -триг-гера в IK- триггере сигналы 1 могут одновременно прийти на входы I и К. При этом состояние триггера изменяется на противоположное, т. е. при I=К схема ведет себя как триггер со счетным входом.

Функцию переходов IK -триггера можно представить в виде булевой функции

Q{t+1) = K(t)Q(t) V I(t)Q(t).. (6.6)

При условии RS=1 IK -триггер удобен тем, что при различных вариантах подключения его входов можно получить схемы функ-

Рис. 6.14. D-триггер

Рнс. 6.15. IK -триггеры

ционирующие как RS, D, T -триггеры (рис. 6.15, б). Вариант построения схемы IK -триггера дан на рис. 6.15, в. Выпускаются IK -триггеры К155ТВ1 и др.

Дата добавления: 2015-08-27; просмотров: 323 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| СИСТЕМА СИНХРОНИЗАЦИИ ЦИФРОВЫХ УСТРОЙСТВ | | | РЕГИСТРЫ, ШИФРАТОРЫ, ДЕШИФРАТОРЫ |