Читайте также:

|

Основные характеристики. Цифровое устройство, преобразующее дискретную информацию, в общем случае имеет n входных и т выходных сигналов алфавита в двоичной форме [5].

Это преобразование осуществляется логическими схемами.· комбинационными схемами и цифровыми автоматами.

В комбинационных схемах (КС) совокупность выходных сигналов (выходное слово Y) в любой момент времени однозначно определяется комбинацией входных сигналов — входным словом X (рис. 6.4).

Закон функционирования КС определен, если задано соответствие между ее входными и выходными словами, например в виде таблицы или в аналитической форме с использованием булевых функций.

Цифровой автомат (ЦА) в отличие от КС имеет некоторое конечное число различных внутренних состояний. Выходное слово Y ЦА в данном такте определяется в общем случае входным словом X и внутренним состоянием автомата, определяемым входным воздействием в предыдущие такты.

ЦА содержит память из запоминающих элементов (ЗЭ) —

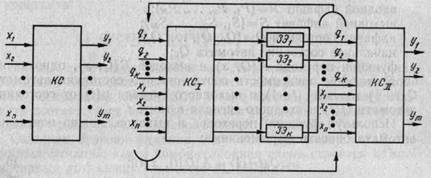

Рис. 6.4. Комбинационная схема Рис. 6.5. Цифровой автомат

триггеров, устройств задержки и др., фиксирующих состояние, в котором он находится.

Комбинационные схемы не содержат ЗЭ, поэтому их называют автоматами без памяти или примитивными автоматами.

Структурная схема ЦА (рис. 6.5) содержит запоминающие элементы ЗЭ 1— ЗЭ К и комбинационные схемы КС I и КС II.

Состояния ЗЭ, определяющие состояние автомата, передаются в форме сигналов qK по цепям прямой связи на входы КС II и по цепям прямой обратной связи на входы КС I. На входы комбинационных схем поступают также сигналы х1..., хп с входов ЦА.

Выходное слово (у1,..., ут) вырабатывается в КС II, причем входными переменными для нее служит алфавит — входное слово (х1,..., хп) и состояния ЗЭ — состояние автомата. Выходные сигналы KC I переводят автомат (его ЗЭ) в новое состояние, при этом входными переменными для этой схемы служит алфавит входного слова и состояния ЗЭ.

Одновременность появления новых значений входных сигналов на всех входах устройства достигается при помощи такти-

рующих сигналов (синхросигналов), обеспечивающих передачу информации с ЗЭ на входы комбинационной схемы одновременно с сигналами, поступающими на ее входы с других устройств.

При анализе автомата его заменяют автоматом с одним эквивалентным входом x(t) и одним эквивалентным выходом

У (t).

Считается, что эквивалентные входной x(t), выходной y(t) сигналы принимают значения из преобразованных алфавитов Ρ и S входных и выходных сигналов.

Для задания ЦА должны быть указаны:

входной алфавит Р={Р1, Р2..., ΡN};,

выходной алфавит S={ S1, S2..., SM};

алфавит состояний Q = {Q1, Q2..., QT};

начальное состояние автомата Qo;

функции перехода A(Q, x) и выходов B(Q, x), однозначно определяющие зависимость соответственно состояния автомата Q(t+1) в такте (t +1) и выходного сигнала y(t) от состояния автомата Q(t) и входного сигнала в такте t.

Используя функции переходов и выходов, можно поведение автомата описать выражениями:

Q(t+1) = A[Q(t), x(t)]; (6.2)

y(t) = B[Q(t), x(t)], (6.3)

где t=0, 1,2,...; Q(0)=QQ.

Выражениям (6.2) и (6.3) соответствует автомат, выходной сигнал которого зависит от состояния автомата и от сигнала на его входе.

В устройствах ЭВМ применяют ЦА, у которых выходной сигнал y(t) в такте t зависит исключительно от состояния автомата Q(t) в этом такте и не зависит от входного сигнала x(t).

Описание законов функционирования комбинационных схем. Используется математический аппарат булевых функций. Переменные х1, x2,..., x п называются двоичными, если они могут принимать только два значения, 0 и 1, а функция от двоичных переменных f(x1, x2,..., хп) называется булевой, если она, так же как и ее аргументы принимает только два значения, 0 и 1.

Система булевых функций W называется функционально полной, если для любой булевой функции f(x1,..., xп) может быть построена равная ей функция путем суперпозиции функций х1,..., хп и функций системы W, взятых в любом конечном числе экземпляров каждая.

Доказано, что если система булевых функций содержит функции логического умножения у = x1x2 или у = x1 /\ x2 (конъюнкция), логического сложения у=x1 \/ x2 (дизъюнкция), опера-

цию отрицания у = х (инверсия), то она является функционально полной.

Функционально полными являются также булевы функции: И—НЕ («штрих Шеффера») Υ=(x1x2), ИЛИ — НЕ («стрелка

ПИРСА») y=(x1 \/ x2) и др.

Техническим аналогом булевой функции является комбинационная схема, выполняющая соответствующее этой функции преобразование информации.

Постоянные уровни напряжения, соответствующие сигналам 0 и 1, рассматриваются как технические аналоги константы 0 и константы 1.

6.3. СИСТЕМЫ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Схемы логических элементов. Логические операции над двоичными переменными реализуются схемами — комбинационными логическими элементами. Число входов логического элемента соответствует числу аргументов (x1, x2,..., xn) воспроизводимой одной или нескольких булевых функций.

Сложная булевая функция получается суперпозицией более простых функций, как и комбинационная схема строится из элементарных логических элементов И, ИЛИ, НЕ.

Последовательное соединение комбинационных логических элементов, при котором выход одной схемы соединен с входом другой схемы, соответствует подстановке в булевые функции в качестве аргументов других булевых функций.

Пересоединение на входах комбинационных схем соответствует перестановке аргументов булевых функций.

Используются также логические элементы, реализующие функции элементарных автоматов.

Схемы связей между различными логическими элементами называют функциональными, где сами элементы изображаются прямоугольниками, в которые вписаны символы реализуемых функций. Выход отмечается кружком, если функция реализуется с инверсией. Примеры схем реализации булевых функций представлены на рис. 6.6.

В логическом элементе И сигнал на выходе у= 1 только в том случае, если одновременно все сигналы на входе равны 1. Если хотя бы один из входных сигналов будет 0, то и выходной сигнал будет 0.

В логическом элементе ИЛИ сигнал на выходе у=1 будет в том случае, если все или часть входных сигналов равны 1, или даже один сигнал равен 1. В элементе НЕ у = 0 при х=1, у= 1 при x =0.

В ЭВМ в качестве элементарных автоматов используются главным образом триггеры.

Передача информации от элемента к элементу может осуществляться несинхронизируемым (асинхронным) способом, причем входные сигналы логических элементов преобразуются с небольшой задержкой в выходные сигналы.

При синхронизируемом способе передачи информации входные сигналы воздействуют на запоминающие логические элементы в определенные моменты времени, соответствующие появлению синхронизирующих сигналов.

Системы логических элементов. Эти системы представляют собой комплекс или серию логических элементов для построения

Рис. 6.6. Схемы реализации функций И, ИЛИ, НЕ

цифровых устройств, объединенных общими электрическими, конструктивными и технологическими параметрами, использующих единый способ представления информации, одинаковый тип межэлементных связей.

Системы элементов содержат элементы для выполнения логических операций, запоминающие элементы, элементы с функцией узлов ЭВМ, а также элементы для усиления, восстановления и формирования сигналов стандартной формы. Элементы представляют собой микросхемы, сформированные в кристалле кремния при помощи специальной технологии. Выпускаются микросхемы малой степени интеграции (ИС), средней степени интеграции (СИС), большой степени интеграции (БИС).

Микросхемы ИС реализуют совокупность логических операций таких как И, ИЛИ, И —ИЛИ, И —НЕ, ИЛИ — НЕ, И — ИЛИ — НЕ и триггеры. Логические элементы на микросхемах СИС, БИС реализуют узлы цифровой автоматики и ЭВМ.

Технические характеристики и режимы эксплуатации цифровых интегральных схем определяются структурой и параметрами их базовых элементов.

Интегральные схемы ИС, СИС — это элементы транзистор-нотранзисторной логики (ТТЛ), или элементы транзисторной логики с эмиттерными связями (ЭСЛ), или интегральные микросхемы на МОП-транзисторах (металл — окисел — полупроводник).

Микросхемы на МОП-транзисторах технологичны, дешевы, находят применение в цифровых устройствах, не требующих очень высокого быстродействия, а также в устройствах с очень

высокой степенью интеграции, например в устройствах памяти.

Элементная база БИС, микропроцессоров строится на разных технологиях и принципах. Наибольшей простотой изготовления отличаются БИС на транзисторах с индуцированным каналом р -типа, но их быстродействие невысоко. По р -МДП-технологии отечественная промышленность выпускает микропроцессорный комплект серии К536.

Более лучшие характеристики имеют БИС на МДП-транзи-сторах n -типа серий К580, К581, К586.

Комплиментарные большие интегральные схемы КМДП БИС выпускаются серий К587, К588.

Самыми быстродействующими являются БИСна логических схемах с эмиттерными связями (ЭСЛ), на основе которых выпускаются БИС серии КР1800.

Перспективными являются интегральные инжекционные логические схемы (И2Л), по которым выполнены БИС серий К582, К583.

Дата добавления: 2015-08-27; просмотров: 579 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Глава 6 ЭЛЕМЕНТЫ И УЗЛЫ ЦИФРОВОЙ АВТОМАТИКИ | | | СИСТЕМА СИНХРОНИЗАЦИИ ЦИФРОВЫХ УСТРОЙСТВ |