Читайте также:

|

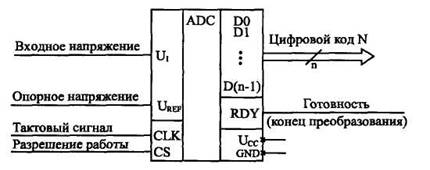

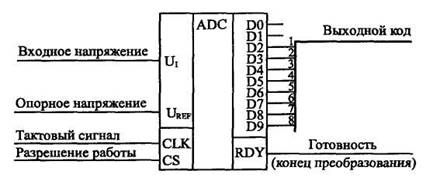

Мікросхеми АЦП виконують функцію, прямо протилежну функції ЦАП - перетворять вхідний аналоговий сигнал в послідовність цифрових кодів. В загальному випадку мікросхему АЦП можна представити у вигляді блоку, що має один аналоговий вхід, один або два входи для подачі опорної (зразкового) напруги, а також цифрові виходи для видачі коду, відповідного поточному значенню аналогового сигналу (малюнок 27.13).

Малюнок 27.13. Мікросхема АЦП.

Часто мікросхема АЦП має також входи для подачі тактового сигналу CLK, сигналу дозволу роботи CS і вихід для видачі сигналу RDY, вказуючого на готовність вихідного цифрового коду. На мікросхему подається одна або дві живлячі напруги. В цілому мікросхеми АЦП складніші, ніж мікросхеми ЦАП, їх різноманітність помітно більша, і тому сформулювати для них загальні принципи використання складніше.

Опорна напруга АЦП задає діапазон вхідної напруги, в якій проводиться перетворення. Вона може бути постійною або ж допускати зміну в деяких межах. Іноді передбачається подача на АЦП двох опорних напруг з різними знаками, тоді АЦП здатний працювати як з позитивними, так і з негативними вхідними напругами.

Вихідний цифровий код N (n-розрядний) однозначно відповідає рівню вхідної напруги. Код може приймати 2п значень, тобто АЦП може розрізняти 2п рівнів вхідної напруги. Кількість розрядів вихідного коду п є найважливішою характеристикою АЦП. У момент готовності вихідного коду видається сигнал закінчення перетворення RDY, по якому зовнішній пристрій може читати код N.

Управляється робота АЦП тактовим сигналом CLK, який задає частоту перетворення, тобто частоту видачі вихідних кодів. Гранична тактова частота - другий найважливіший параметр АЦП. В деяких мікросхемах є вбудований генератор тактових сигналів, тому до їх виводів підключається кварцовий генератор або конденсатор, задаючий частоту перетворення. Сигнал CS дозволяє роботу мікросхеми.

Випускається безліч найрізноманітніших мікросхем АЦП, що розрізняються швидкістю роботи (частота перетворення від сотень кілогерців до сотень мегагерц), розрядністю (від 6 до 24), допустимими діапазонами вхідного сигналу, величинами погрішностей, рівнями живлячих напруг, методами видачі вихідного коду (паралельний або послідовний), іншими параметрами. Звичайно мікросхеми з великою кількістю розрядів мають невисоку швидкодію, а самі швидкодійні мікросхеми мають невелике число розрядів. Область вживання будь-якої мікросхеми АЦП багато в чому визначається використаним в ній принципом перетворення, тому необхідно знати особливості цих принципів. Для вибору і використовування АЦП необхідно користуватися докладними довідковими даними від фірми-виробника.

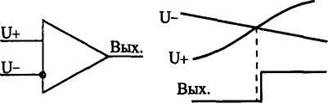

Малюнок 27.14. Компаратор напруги.

Як базовий елемент будь-кого АЦП використовується компаратор напруги (малюнок 27.14), який порівнює дві вхідні аналогові напруги і залежно від результату порівняння видає вихідний цифровий сигнал нуль або одиницю. Компаратор працює з великим діапазоном вхідних напруг і має високу швидкодію (затримка порядку одиниць наносекунд).

Існує два основні принципи побудови АЦП: послідовний і паралельний.

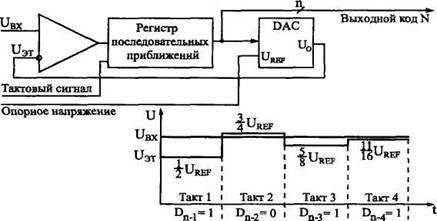

В послідовному АЦП вхідна напруга послідовно порівнюється одним єдиним компаратором з декількома еталонними рівнями напруги, і в залежності від результатів цього порівняння формується вихідний код. Найбільше поширення набули АЦП на основі так званого регістра послідовних наближень (малюнок 27.15).

Малюнок 27.15. АЦП послідовного типу.

Вхідна напруга подається на вхід компаратора, на інший вхід якого подається еталонна напруга, що східчасто змінюється в часі. Вихідний сигнал компаратора подається на вхід регістра послідовних наближень, тактованого зовнішнім тактовим сигналом. Вихідний код регістра послідовних наближень поступає на ЦАП, яке з опорної напруги формує змінну еталонну напругу.

Регістр послідовних наближень працює так, що залежно від результату попереднього порівняння вибирається наступний рівень еталонної напруги по наступному алгоритму:

Зрозуміло, що цей процес досить повільний, вимагає декількох тактів, причому протягом кожного такту повинні встигнути спрацювати компаратор, регістр послідовних наближень і ЦАП з виходом по напрузі. Тому послідовні АЦП досить повільні, мають порівняно великий час перетворення і малу частоту перетворення.

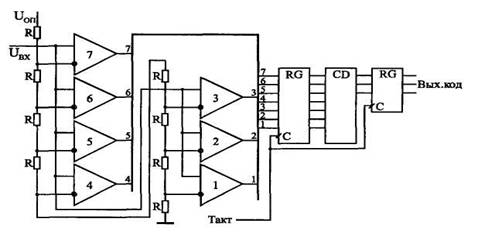

Другий тип АЦП, АЦП паралельного типу, працює за більш простим принципом. Всі розряди вихідного коду обчислюються в них одночасно (паралельно), тому вони набагато швидші, ніж послідовні АЦП. Правда, вони вимагають вживання великої кількості компараторів (2П - 1), що викликає чисто технологічні труднощі при великій кількості розрядів (наприклад, при 12-розрядному АЦП потрібні 4095 компараторів).

Схема такого АЦП (малюнок 27.16) включає резистивный дільник з 2П однакових резисторів, який ділить опорну напругу на (2П- 1) рівнів.

Вхідна напруга порівнюється за допомогою компараторів з рівнями, формованими дільником напруги. Вихідні сигнали компараторів за допомогою шифратора перетворяться в n-розрядний двійковий код. Шифратор видає на вихід номер останнього з компараторів, що спрацювали (тобто тих що видали сигнал логічної одиниці). Наприклад, у разі 3-розрядного АЦП (на малюнку) при величині вхідної напруги від 0 до 1/8 опорної напруги вихідний код буде 000, при вхідній напрузі від 1/8 до 2/8 опорної напруги спрацює перший компаратор, що дасть вихідний код 001, при вхідній напрузі від 2/8 до 3/8 опорної напруги спрацюють компаратори 1 і 2, що дасть вихідний код 010, і т.д. Процес перетворення відбувається в паралельному АЦП дуже швидко, тому частота перетворення може досягати сотень мегагерц.

Для підвищення швидкодії в паралельному АЦП іноді застосовується конвейєрний принцип: вихідний код компараторів записується в (2П -1) -розрядний паралельний регістр, показаний на малюнку 27.16. Вихідний код шифратора також записується в n-разрядный паралельний регістр. Обидва регістри в цьому випадку тактуються одним і тим же тактовим сигналом. Це знижує вимоги до швидкодії компараторів і шифратора. Правда, вихідний код АЦП затримується через такі регістри на два періоди такої частоти.

Малюнок 27.16. 3-розрядний АЦП паралельного типу.

Громіздкість структури паралельного АЦП призводить до того, що в деяких АЦП застосовується змішаний паралельно-послідовний принцип. Це дещо знижує швидкодію подібного АЦП в порівнянні із звичайним паралельним АЦП, та зате дозволяє одержати велике число розрядів, не збільшуючи кількість компараторів до 2п-1.

Для того, щоб АЦП будь-якого типу працював з використанням всіх своїх можливостей, необхідно забезпечити узгодження діапазону зміни вхідного аналогового сигналу з допустимим діапазоном (динамічним діапазоном) вхідної напруги АЦП.

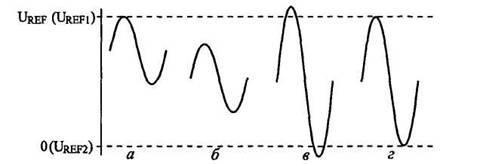

Малюнок 27.17. Співвідношення вхідного сигналу і динамічного діапазону АЦП.

На малюнку 27.17 показано чотири можливі випадки співвідношення динамічного діапазону АЦП (від 0 до Uref або від Uref1 до Uref2) і вхідного сигналу. У випадках а і б вхідний сигнал менше динамічного діапазону, тому АЦП працюватиме правильно, але не використовуватиме всіх своїх можливостей. У випадку в вхідний сигнал дуже великий, тому частина його значень не буде перетворена. Тільки у разі г АЦП дійсно працювати як n-розрядний і перетворюватиме всі значення вхідного сигналу. Для узгодження вхідного сигналу з динамічним діапазоном АЦП можна застосовувати підсилювачі, аттенюатори, схеми зсуву. В деяких випадках узгодження може бути досягнуте простим вибором величин опорних напруг.

Іноді необхідно зменшити кількість розрядів АЦП. В цьому випадку потрібна кількість молодших розрядів вихідного коду мікросхеми просто не використовується. На малюнку 27.18 показано використовування 10-розрядного АЦП як 8-розрядного.

Малюнок 27.18. Зменшення кількості розрядів вихідного коду АЦП.

Зворотна задача - збільшення розрядності АЦП - зустрічається частіше. Існує ряд типових рішень схемотехнік по об'єднанню декількох мікросхем АЦП для збільшення кількості розрядів вихідного коду, але більшість цих рішень вимагає складних розрахунків результуючих погрішностей перетворення і вживання аналогових вузлів. Ми не будемо їх тут розглядати. Відзначимо тільки, що при виникненні задачі збільшення розрядності треба перш за все спробувати знайти мікросхему з потрібною кількістю розрядів і тільки потім розглядати можливості об'єднання декількох мікросхем АЦП.

Розглянемо декілька типових схем включення АЦП, що використовуються в аналого-цифрових системах.

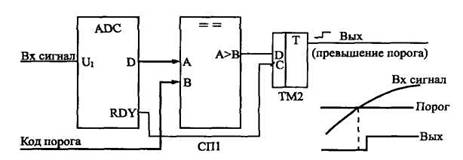

Малюнок 27.19. Фіксатор перевищення вхідним сигналом встановленого порогу

Перша схема (малюнок 27.19) призначена для фіксації моменту перевищення вхідним аналоговим сигналом заданої порогової напруги. Схема виробляє вихідний сигнал (позитивний фронт) тоді, коли вхідний аналоговий сигнал стає більше встановленого рівня, причому цей рівень задається цифровим кодом порогу. Код порогу порівнюється з вихідними кодами АЦП за допомогою мікросхеми компаратора кодів. Вихідний сигнал компаратора кодів записується в трігер по сигналу RDY з АЦП, що дозволяє виключити вплив коротких імпульсів, що виникають на виході компаратора у момент зміни вхідних кодів. Вживання цього трігера затримує вихідний сигнал на один такт.

Може здатися, що вживання АЦП в даному випадку не виправдано, надмірно. Але треба враховувати, що в аналого-цифрових системах АЦП, перетворюючий вхідний сигнал в послідовність кодів, як правило, вже є, тому додаткового АЦП не потрібно, достатньо тільки включити компаратор кодів і трігер.

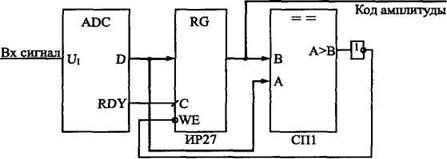

АЦП також застосовується в схемах обчислення амплітуди вхідного аналогового сигналу Для такого обчислення можна використовувати вже розглянуту схему обчислювача екстремального значення вхідного коду. Як джерело послідовності вхідних кодів в даному випадку виступає АЦП (малюнок 27.20).

Малюнок 27.20. Обчислювач амплітуди аналогового сигналу

В регістр з входом дозволу запису записується код з виходу АЦП по сигналу RDY в тому випадку, якщо поточне значення коду більше значення коду, записаного раніше в регістр. В результаті вже після одного періоду вхідного сигналу в регістрі буде код амплітуди вхідного сигналу. За період перетворення АЦП повинні встигнути спрацювати компаратор кодів і регістр.

Якщо такий обчислювач амплітуди вхідного сигналу використовується у складі складної аналого-цифрової системі, в якій вже присутній АЦП, безперервно перетворюючий вхідний сигнал в коди, то додатково потрібні тільки цифрові мікросхеми: компаратор кодів і регістр.

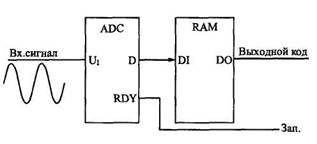

Використовування АЦП, що часто зустрічається, - це перетворення вхідного сигналу в потік кодів, причому коди ці звичайно записуються в буферну пам'ять. В даному випадку самим відповідним є однонаправлений буфер з періодичним режимом роботи. Тобто спочатку в буферну пам'ять заноситься масив кодів вибірок вхідного сигналу, а потім цей масив читається для подальшої обробки Саме так наприклад, будується цифровий осцилограф, призначений для спостереження аналогових сигналів на екрані.

Схема включення АЦП в цьому випадку показана на малюнку 27.21. Як строб запису в буферну пам'ять використовується сигнал RDY з АЦП. Докладніше організацію буфера ми вже розглядали в попередньому розділі.

Звичайно, в реальних аналого-цифрових пристроях все набагато складніше, в них потрібні схеми синхронізації процесу запису з вхідним сигналом, схеми попередньої обробки аналогового сигналу, але суть залишається тією ж - буферна пам'ять, записуюча послідовність кодів з виходу АЦП. Чим більше об'єм пам'яті, тим більший фрагмент вхідного аналогового сигналу вона може запам'ятати. Наприклад, якщо пам'ять має організацію 64К X 8 і працює з 8-розрядним АЦП, то при частоті перетворення АЦП 10 Мгц буфер зможе берегти в собі фрагмент аналогового сигналу тривалістю 6,5536 мс.

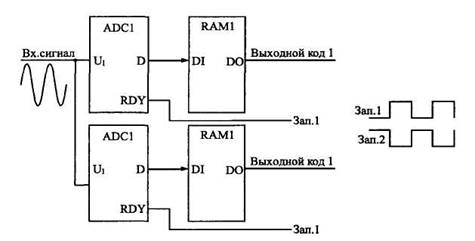

Нарешті, остання схема, яку ми розглянемо (малюнок 27.22), дозволяє удвічі підвищити швидкодію АЦП, точніше, підняти удвічі частоту запису кодів вибірок вхідного сигналу в буферну пам'ять.

Малюнок 27.21. Включення буферної пам'яті для запам'ятовування кодів з виходів АЦП.

Малюнок 27.22. Збільшення удвічі частоти перетворення вхідного сигналу за допомогою двох АЦП з буферами.

Ідея схеми дуже проста: використовується два АЦП і два буфери, які працюють по черзі, наприклад, парні вибірки вхідного сигналу обробляє один АЦП з своїм буфером, а непарні - інший АЦП з своїм буфером. В результаті запам'ятовування кодів вхідного сигналу здійснюється з частотою удвічі більше частоти перетворення кожного з АЦП. Наприклад, якщо кожний АЦП і кожний буфер працюють з частотою 10 Мгц, то результуюча частота перетворення складе 20 Мгц.

Тактові сигнали АЦП і сигнали RDY на виходах АЦП повинні бути зсунуті один щодо іншого на половину періоду тактового сигналу. Читання зареєстрованих кодів з обох буферів також повинне бути організовано по черзі: перший код читається з першого буфера, другий - з другого, третій - знову з першого, четвертий - з другого і т.д. Об'єм обох буферів в даному випадку складається. Наприклад, при організації кожного буфера 64К X 8 результуючий буфер матиме організацію 128К X 8.

Користуючись цим же принципом, можна підвищити частоту обробки вхідного сигналу за допомогою АЦП не тільки удвічі, але і втричі, в чотири рази і т.д. Необхідно тільки погодити в часі роботу відповідно трьох, чотирьох і т.д. АЦП, у кожного з яких повинна бути своя буферна пам'ять.

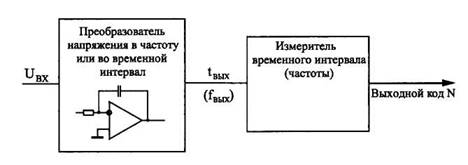

Крім згаданих тут АЦП послідовно і паралельного типів існують ще і АЦП з проміжним перетворенням. В них вхідний аналоговий сигнал за допомогою аналогового інтегратора перетвориться в часовий інтервал між цифровими імпульсами або в частоту проходження цифрових імпульсів. Вихідний цифровий код, відповідний вхідному аналоговому сигналу формується в результаті вимірювання тривалості тимчасового інтервалу або частоти проходження імпульсів (малюнок 27.23). Якщо використовується вихідна частота, то такий АЦП називається «перетворювачем напруга- частота» (ПНЧ).

Малюнок 27.23. АЦП з проміжним перетворенням.

Такий підхід дозволяє за допомогою порівняно простих апаратних засобів одержати високу точність перетворення, не залежну від багатьох параметрів компонентів, що використовуються, і від характеристик навколишнього середовища.

В кінці треба ще раз відзначити, що приведені тут схеми сильно спрощені, для їх практичної реалізації необхідне знання не тільки цифрової схемотехніки, але і аналогової і аналого-цифрової схемотехніки, а також знання особливостей конкретних мікросхем ЦАП і АЦП. Проте розглянуті тут ключові принципи використовування ЦАП і АЦП і їх сумісного включення з цифровими схемами будуть корисні будь-якому розробнику.

Дата добавления: 2015-08-21; просмотров: 117 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Ментальная блокировка | | | Тема 2. Характеристика гостиничных предприятиЙ |