Читайте также:

|

Основные характеристики. Микропроцессор К580ИК80 размещен в корпусе с 46 выводами. Структурная схема представлена на рис. 7.1. Назначение и номера внешних выводов приведены в табл. 7.2.

МП К580ИК80 имеет одну 8-разрядную внутреннюю шину, которая связывает все функциональные блоки операционной части. В состав МП входят: 8-разрядное АЛУ со схемами деся-

тичной коррекции (СДК); восемь 8-разрядных ΡΟΗ (W, Ζ, Β, С, D, Ε, Η, L); 8-разрядный аккумулятор А и два буферных регистра БР, БР2; 4-разрядный регистр признаков РП; 8-разрядный регистр команды РК; 16-разрядный регистр — про-

Рис. 7.1. Схема микропроцессора К580ИК80

граммный счетчик (ПС); 16-разрядный регистр — указатель стека УС; схема инкремента-декремента СИД.

МП связан с внешними устройствами 8-разрядной двунаправленной шиной данных ШД (Д0.. .Д 7 ) и 16-разрядной шиной адреса ША (А 0... А 15), которая позволяет адресовать 64 Кбайт памяти. Связь с внешними шинами данных и адреса осуществляется через специальные вентильные буферные регистры, имеющие три состояния.

| № вывода | Обозначение (рис. 7.1) | Наименование | Примечание | |

| 7... 9 11... 23 | ША | Шина адреса [0... 15] | Выход | |

| 26... 28 31... 35 | ШД | Шина данных [0... 7] | Вход/выход | |

| 2,40 | Cl, C2 | 2 Серии непересекающихся синхроимпульсов | Вход | |

| ЗПР | Вход запроса на прерывание | Вход | ||

| РПР | Разрешение прерывания | В ыход | ||

| ЗХ | Запрос ВнУ на захват шин | Вход | ||

| ПЗХ | ПРИЕМ ЗАХВАТА | Выход | ||

| 3. | ГОТ | Признак готовности ВнУ к обмену | Вход | |

| ОЖД | Признак ожидания МП готовности ВнУ | Выход | ||

| СБР | Перевод МП в исходное состояние (сброс) Прием | Вход | ||

| ЧТ (ПМ) | Чтение данных с внешней шины (ВЫДАЧА) | Выход | ||

| ЗП(ВД) | Запись данных на внешнюю шину | Выход | ||

| С | СИНХРОНИЗАЦИЯ | Выход | ||

| 6, 24, 46 | — | Питание (+12,5 В, —5 В, +5 В) | Вход | |

| — | ОБЩИЙ | — |

Управляющая часть МП включает в себя дешифратор команд ДШК, схему управления машинным циклом СУМЦ, схему выбора регистров ΡΟΗ (СВР), блок управления БУ, блок синхронизации БС и блок управления обменом БУОБ.

На вход блока синхронизации поступают 2 серии непересекающихся импульсов (С 1 и С2), им вырабатывается выходной сигнал С, который означает начало 1-го такта каждого машинного цикла команды МП.

С помощью сигналов запроса на прерывание ЗПР, захвата шин ЗХ и ответных сигналов МП (РПТ, ПЗХ) или организуется обслуживание запроса внешних устройств, или осуществляется допуск внешних устройств к шинам данных и адреса, т. е. отключение МП от этих шин при помощи вентильных схем [БД и БА), имеющих три состояния (одно из них — отключение от шин).

На вход БУОБ поступают также сигнал ГОТ, являющийся признаком готовности внешнего устройства к обмену информацией. Ожидание этого сигнала ГОТ подтверждается выходным сигналом ОЖД.

По сигналу СБР МП устанавливается в начальное состояние, в частности устанавливается в нуль программный счетчик

ПС. С помощью ЧТ и ЗП микропроцессор извещает ОЗУ или внешние устройства о характере операции обмена (приеме или выдаче данных).

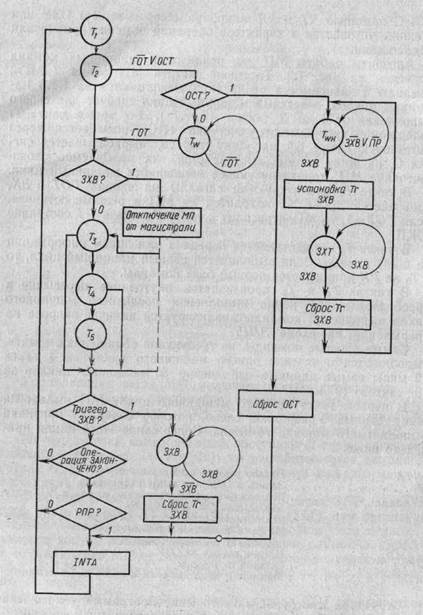

Алгоритм работы МП по реализации машинных команд приведен на рис. 7.2. Тактовая частота МП равна 2 МГц, команды в зависимости от их типа выполняются за 1...5 машинных циклов, а каждый машинный цикл требует для своего выполнения от 3 до 5 тактов (T 1.. T 5). Во время такта T 1 содержимое программного счетчика (ПС) посылается через вентильную схему БА на шину адреса, вырабатывается сигнал С, на шину данных выставляется так называемое слово-состояние МП, характеризующее начавшийся машинный цикл.

В такте Т2 анализируются сигналы на входах ГОТ и ЗХ, проверяется также, не находится ли МП в режиме останова. Если ГОТ=1, то МП переходит к такту Т 3, иначе — в состояние

ОЖД

В такте Т 3 осуществляется передача или прием информации на шину данных. Если выполняется первый машинный цикл, то в Т 3 на РК принимается первый байт команды.

В тактах Т 4 и Т5 производятся внутренние пересылки и преобразования. В конце выполнения последнего машинного цикла выполнения команды анализируется наличие запроса на прерывание на входе ЗПР.

Самые простые команды, не требующие обращения к памяти, выполняются в течение одного машинного цикла за 4 такта (2 мкс); самые длинные — в течение 5 машинных циклов за 18 тактов (9 мкс).

В первом такте каждого машинного цикла МП выдает на шину данных 8-разрядное слово, которое содержит признаки выполняемого машинного цикла. Содержание этого цикла приведено ниже.

INTA........Начало реакции на прерывание

W...........Запись в ОЗУ или вывод информации

OUT.........ША содержит адрес устройства вывода, а ШД содержит выводимую информацию

IN Ρ.........ША содержит адрес устройства ввода, а на ШД должны быть помещены вводимые данные

STACK........Обращение к стековой памяти

MEMR........Чтение данных из ОЗУ

HLTA.........Останов по команде

M 1..........Машинный цикл выборки первого байта команды

Структура многокристального микропрограммируемого микропроцессора. Рассмотрим состав и структуру микропроцессорного набора серии 1804, выполненного по технологии ТТЛШ. Состав серии в табл. 7.3.

Структура микропроцессорной секции 1804 ВС1 (МПС) представлена на рис. 7.3 и имеет следующие особенности: воз-

Рис. 7.2. Алгоритм работы МП К580ИК80 по реализации машинных команд

можность наращивания разрядности (n ×4); регистровые запоминающие устройства 16 четырехразрядных слов с двумя каналами считывания (РЗУ); специальный регистр с собственными цепями сдвига (P Г Q); сдвигатель данных для результата операций АЛУ при записи информации в РЗУ; выработка в АЛУ признаков (переноса, переполнения, знака и нулевого результата); наличие трехстабильной шины вывода; наличие 2 пар двунаправленных шин сдвига.

4-разрядные АЛУ выполняют операции с операндами, поступающими на входы R и S, результат выдается по выходу F.

Таблица 7.3

| Обозначение | Наименование | Количество выводов | Мощность, Вт |

| 1804 ВС1 | Микропроцессорная секция (МПС) — 4 разряда | ||

| 1804 ВУ1 | 4-разрядные секции управления адресом микрокоманд (СУАМ 1) | 0,5 | |

| 1804 ВУ2 | 4-разрядные секции управления адресом микрокоманд (СУАМ 2) | 0,5 | |

| 1804 ВУЗ | Схема управления следующим адресом (УСА) | 0,5 | |

| 1804 ВР1 | Схема ускоренного переноса | 0,3 | |

| 1804 ИР 1 | 4-разрядный регистр | 0,5 |

АЛУ вырабатывают признаки: Ζ (нулевой результат), OUR (переполнение), F3 (старший разряд, знак числа), С4 (перенос). На вход в АЛУ также поступает сигнал С0 — входной перенос. Кроме того, АЛУ формирует сигналы G и Ρ (генерации и распространения), которые используются для организации ускоренного переноса в многоразрядной секции при помощи схемы 1804 ВР1.

При помощи схемы селектора источника данных СИД выбирается два операнда из возможных пяти источников: Д (внешние данные с ШД), А или В (выходы регистров РгА и РгВ регистрового запоминающего устройства), Q (регистр РгQ.) или 0(нулевой код). Считывание из РЗУ производится из регистров, адреса которых устанавливаются на адресных входах А0...A3 и В0...ВЗ. Перед записью в РЗУ и PгQ информация может быть сдвинута влево и вправо с помощью сдвига-телей СДА и СДР. Сигналы PR0, PRS и PQ0, PQS на двунаправленных 3 стабильных выводах МПС устанавливаются при сдвигах перед записью в РЗУ и PгQ.

Схема выбора данных СВД определяет приемник результата. На выходную трехстабильную шину данных (У0...У3) может быть подан результат с выхода F АЛУ или с регистра

РгА (РЗУ). Управление выходными вентилями осуществляется сигналом (ОЕ). Управление 1804 ВС1 осуществляется разрядами (10...18) микрокоманды, которые при помощи дешифраторов определяют операцию АЛУ (13...15), источник данных (10... 12) и приемник результата АЛУ (16... 18). Управление производится в соответствии с табл. 7.4.

Структура секции управления адресом микрокоманды 1804ВУ1, 1804ВУ2 (СУАМ) представлена на рис. 7.4. Основные блоки СУАМ. Блок выборки адреса содержит мультиплексор, при помощи сигналов S0, S1 выбирается источник адреса следующей микрокоманды (РгА, стек РгСМК, выходы Д0...Д3).

Рис. 7.3. Структура микропроцессорной секции 1804 BCI

На выходе мультиплексора при помощи схем ИЛИ (4×1) адрес микрокоманды можно модифицировать при помощи маски на входах OR0...OR3.

При ΖA=0 на выходе СУАМ устанавливается нулевой код.

Таблица 7.4

| Микрокод | Источник операндов АЛ У (12, 11. 10) | Операции АЛ У (15, 14, 13) | Приемник результата (18, 17, 16) | ||||||||

| РЗУ | PгQ | у | |||||||||

| Сдвиг | Загрузка | Сдвиг | Загрузка | Выход | |||||||

| R | | S | ||||||||||

| А | Q | R + S +С0 | — | — | — | P→Q | Ε | ||||

| А | В | S-R-1 + С0 | — | — | — | — | F | ||||

| Q | R-S-1 + С 0 | — | F→B | — | — | А | |||||

| В | RVS | — | F→B | — | — | F | |||||

| А | R∙S | Вправо | F/2→B | Вправо | Q/2→ Q | F | |||||

| D | А | R∙S | Вправо | F/2→B | — | — | F | ||||

| D | Q | R+S | Влево | 2F→B | Влево | 2Q→Q | F | ||||

| D | (R + S) | Влево | 2F→B | — | F |

Счетчик микрокоманд состоит из регистра РгСМК и схемы приращения ИНК. При С0=\ содержимое счетчика увеличивается на 1.

Стек состоит из накопителя, указателя стека и схем записи, считывания. Глубина стека — 4. Стек управления сигналами

(FE) и PUP.

Регистр РгА служит буфером для хранения адреса, принятого по входам R0 — R3 (для 1804ВУ2 по входам Д0... Д3). Управление записью в РгА производится по сигналу RE. Управление 1804ВУ1, 1804ВУ2 производится сигналами в соответствии с табл. 7.5.

Структура однокристальной микроЭВМ. На одном кристалле размещается совокупность блоков, образующих своего рода микроЭВМ. Например микроЭВМ типа К1801ВЕ1, представленная на рис. 7.5.

Таблица 7.5

| S 1 | S 0 | у | ORi | (ZA) | (OE) | yi | (FE) | PUP | Операция в стеке |

| смк | * | * | Отключено | * | Отключено содержание СМК | ||||

| РгА | * | Записывание в (СтО) | |||||||

| Cт0 | |||||||||

| D | A | Цикл сдвига стека |

Процессор микроЭВМ содержит АЛУ, девять ΡΟΗ, блок микропрограммного управления на основе программируемой логической матрицы (ПЛМ), блок обмена, блок прерываний.

Блок ОЗУ содержит 128 ячеек по 16 разрядов, имеется также ПЗУ с организацией 1024×16. Последовательная магистраль ввода — вывода (4 разр.) состоит из 16 разрядного регистра и блока управления.

Блок согласования с системной магистралью состоит из контроллера прямого доступа к системной магистрали, схем согласования внутренней и системной магистрали. Интерфейс

Рис. 7.4. Структура секции управления адресом микрокоманды К1804ВУ1,

К1804ВУ2 (САУМ)

Рис. 7.5. Схема микроЭВМ К1801ВЕ1

системной магистрали совместим с интерфейсом микроЭВМ «Электроника-60».

Разрядность микроЭВМ КР1801ВЕ1 составляет 16, имеется 404 команды, 8 способов адресации памяти, адресуемость к 64 К-слов (16 разрядных), тактовая частота от 100 кГц до 8 МГц. В составе микроЭВМ имеется таймер.

Дата добавления: 2015-08-27; просмотров: 688 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| КЛАССИФИКАЦИЯ И ХАРАКТЕРИСТИКИ МИКРОПРОЦЕССОРОВ | | | ИНТЕРФЕЙС МИКРОПРОЦЕССОРНЫХ СИСТЕМ |