Лабораторна робота №2. Дослідження дешифратора

Мета: Дослідити характеристики дешифратора, зібрати його схему.

Теоретичні дані

Зворотне перетворення двійкового коду в код «1 з N» виконують перетворювачі коду, звані дешифраторами. Якщо на входи дешифратора подається двійковий код, то на одному з виходів дешифратора виробляється сигнал 1, а на інших виходах зберігаються сигнали 0. У загальному випадку дешифратор з п входами має 2n виходів, так як n-розрядний код вхідного слова може приймати 2n різних значень і кожному з цих значень відповідає сигнал 1 на одному з виходів дешифратора.

На виходах дешифратора з номерами 0, 1, 2,..., 2n-1 виробляються значення булевих функцій відповідно:

Дешифратори встановлюються в схемах ЕОМ та інших цифрових пристроїв на виходах регістрів або лічильників і служать для перетворення коду слова, що знаходиться в регістрі (в лічильнику), в керуючий сигнал на одному з виходів дешифратора, наприклад, для управління входами десяткового (або семисегментного) газорозрядного або напівпровідникового індикатора або елементами вибірки символів друкувального пристрою.

На рис. 1, а показаний спосіб побудови дешифратора на прикладі схеми дешифратора для трирозрядного вхідного слова. Схема являє собою набір з восьми тривхідних елементів І, на входи яких подані всі можливі комбінації прямих і інверсних значень розрядів слова.

Якщо кожен елемент має вхід для сигналу синхронізації, то така схема називається дешифратором зі входом синхронізації (рис. 1, в). Такого виду схеми випускаються в складі комплексів інтегральних логічних елементів.

| Рис.1. Дешифратор с інверсними виходами. а — функциональна схема; б — умовне позначення дешифратора; в умовне позначення дешифратора з входом синхронізації. |

Нарощування розмірності

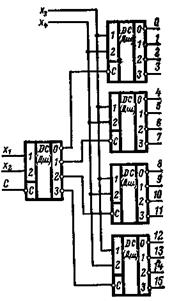

Розглянуті вище схеми дешифраторів відносяться до типу лінійних і для них характерно одноступінчаста дешифрування вхідних n-розрядних кодів за допомогою n-входових логічних елементів. Однак зі зростанням розрядності вхідного коду кількість входів логічних елементів і кількість самих логічних елементів швидко наростає. Тому лінійна структура зазвичай використовується для побудови дешифраторів з n <4. При більшої розрядності вхідного коду дешифратори виконуються за багатоступеневою схемою. При цьому, як правило, використовуються дешифратори з інверсними виходами і інверсними входами синхронізації. Каскадне включення таких схем дозволяє легко нарощувати число дешифрованих змінних. Принцип побудови схем неважко зрозуміти, звернувшись до рис. 2. Тут показаний дешифратор на чотири входи з інверсними виходами, побудований з інтегральних елементів, що реалізують схеми двовхідних дешифраторів.

|

Рис. 2. Каскадний дешифратор

Для отримання потрібних 16 виходів складається стовпець з чотирьох дешифраторів другого ярусу. Дешифратор першого ярусу приймає два старші розряди вхідного коду Х1 і Х2. Збуджений одиничний вихід цього дешифратора відмикає один з дешифраторів стовпця за його входу дозволу. Обраний дешифратор стовпця розшифровує 2 молодших розряду вхідного слова.

Кожному вхідному слову відповідає збудження тільки одного виходу.

Наприклад, при дешифрації слова X1X2X3X4 = 11012 = 1210 на вході дешифратора першого ярусу мається код 11, збудливий його вихід номер три, що дозволяє роботу 4-го зверху дешифратора другого ярусу. На його вході діє код 01, тому одиниця з'явиться на його першому виході, тобто на 12-му виході схеми в цілому, що й вимагається.

Загальні дозвіл чи заборона роботи схеми здійснюється по входу С дешифратора першого ярусу.

Завдання та порядок роботи

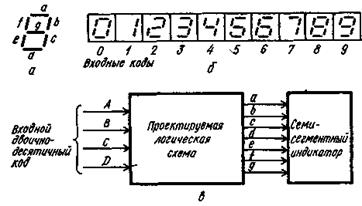

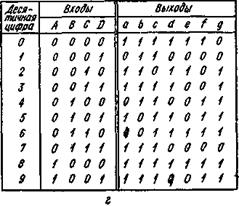

В лабораторній роботі використаємо дешифратор для семисегметного індикатора (рис. 3):

|

Рис. 3

Семисегментний індикатор, схема управління і таблиця відповідності.

Як бачимо, для відтворення деяких цифр використовуються одні й ті ж елементи (сегменти), тобто при різних комбінаціях коду на вході (A, B, C, D) повинен включатися один і той же сегмент. Так у цифр 0, 2, 6, 8 загальним є сегмент е. Розглянемо таблицю відповідності (рис. 3г), в якій з'ясуємо, при яких кодах повинні включатися відповідні сегменти.

Сегмент е (дивимося по вертикалі в таблиці на рис. 3г) включається при кодах на вході:

| A B C D |

| 0 0 0 0 |

| 0 0 1 0 |

| 0 1 1 0 |

| 1 0 0 0 |

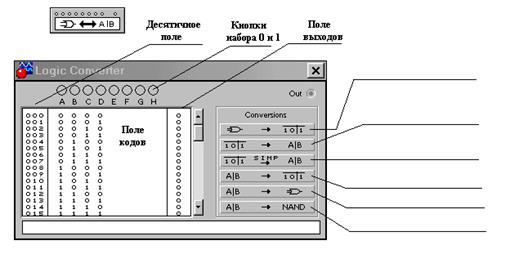

Використовуємо для створення такого коду у вигляді електричних сигналів пристрій Logic Converter з програми Workbench (рис. 4).

Використаємо для створення такого коду сигнали пристрою Logic Converter з програми Workbench (рис. 4).

Рис. 4.

Після набору кодів вхідних сигналів і відповідних їм виходів можна отримати булевий вираз в нижній частині Logic Converter'а, натиснувши на кнопку перетворення таблиці в вираз - друга кнопка зверху в правій частині картинки.

Мінімізація формули проводиться кнопкою SIMP.

Перехід від формули до реалізації у вигляді набору елементарних комірок відбувається при натисканні другої знизу кнопки. Сама нижня кнопка видає схему, набрану на інверсних елементах.

У тому випадку, коли схема займає багато місця на екрані, її слід мінімізувати, згорнувши її в один блок. Для цього необхідно поставити на місці майбутніх входів і виходів точки (клеми), обмежити необхідну частину схеми прямокутником маркера, зайти в меню Circuit> CreateSubcircuit> Name> Replace in circuit (назвати ваш блок у відповідності з виконуваними ним функціями).

Хід роботи

1. Створити дешифратор для семисегментного індикатора, що виконує індикацію цифр від 0 до 9.

2. Ввести в звіт схему «поліпшеного» дешифратора.

Дата добавления: 2015-10-30; просмотров: 149 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Список используемых источников | | | МЕТА І ЗАДАЧІ КУРСОВОГО ПРОЕКТУ |