Читайте также:

|

Курсовой проект

Защищен с оценкой:

Преподаватель: Курсанов О.И.

Блок умножения

Пояснительная записка к курсовому проекту по дисциплине

«Схемотехника ЭВМ»

СЭВМ 42.2201.4121.05 КП

Работу выполнил Мещеров Ринат

Студент гр.4121

Санкт-Петербург

Содержание проекта

Перечень сокращенных буквенных обозначений и символов….4

Введение……………………………………………………………5

Проектное задание…………………………………………………6

1. Выбор функциональной схемы………………………………...6

2. Выбор элементной базы………………………………………...7

2.1 Конструктивное содержание схемы…………………………...9

2.1.1 Блок приема информации в схему и выдачи результата....10

2.1.2 Блок умножения ………………….………………………….10

2.2 Разработка принципиальной схемы устройства….………….11

Выбор платы……………………………………………………..11

4 Моделирование…………………………………………….…….12

5. Разработка конструкции………………………………………..13

5.1 Спецификация……………...…………………………………..14

Заключение………………………………………………………...15

Список использованной литературы……………………………..16

Перечень сокращений буквенных изображений и символов.

КП – курсовой проект.

ИС – интегральная микросхема.

ТТЛ – транзисторно-транзисторная логика.

МОП – Металл, окисел, проводник

нс – наносекунда.

Введение.

Цифровая обработка данных с помощью автоматических устройств является результатом технического прогресса. Еще в средние века были созданы примитивные по современным понятиям решающие устройства, которые могли выполнять такие несложные вычислительные действия, как сложение и вычитание. Эти вычислительные машины, работавшие на чисто механическом принципе, были столь велики и по размерам и дороги, что тогда не могло быть и речи о той популярности, которой пользуются современные ЭВМ.

Развитие технологий позволило существенно снизить объемы и себестоимость вычислительных устройств, что повлекло за собой естественное желание переложить на аппаратную основу как можно большее количество операций, выполняемых ЭВМ, с тем чтобы освободить программиста от решения этих задач вручную (программным способом). В простейшем случае – это операции деления и умножения, в конечном же итоге – аппаратная поддержка процедур обработки графической, звуковой и других видов информации.

Предметом моего курсового проекта стал комбинационный восьмиразрядный блок умножения. Входной информацией служат два восьмиразрядных слова А и В, выходной – слово С (16 разряда), являющееся произведением А и В. Спроектированная схема должна зафиксировать результат в регистре. Необходимо также определить время, за которое схема корректно выдает результат. Эта величина будет зависеть от количества логических элементов, которые информационный сигнал должен пройти, чтобы появиться на выходе последнего сумматора.

В применяющейся системе проектирования электронных схем (MICRO-CAP5) возможно полностью протестировать собранную схему. Система позволяет определять значения информационных сигналов в любой точке схемы, использовать широкий набор интегральных и аналоговых элементов, редактировать и создавать новые их образцы.

Проектное задание.

Требуется спроектировать комбинационный блок умножения двух восьмиразрядных слов следующего вида:

1. Выбор функциональной схемы.

В работе использован стандартный алгоритм умножения.

В схеме используется счетчик который подает осведомительные сигналы устройствам схемы и во вне. При такой реализации быстродействие устройства будет, работа более устойчивой (почти одинаковое число элементов для каждого разряда), что позволит привязать устройство к внешней синхронизации, что является не только достоинством, но и необходимым условием работы схемы в составе ЭВМ.

2. Выбор элементной базы.

Для того чтобы выбрать элементную базу проектируемого устройства необходимо провести сравнительный анализ различных серий микросхем.

Известно, что на первых этапах развития биполярных цифровых микросхем предсказывали широкое распространение комплиментарных биполярных логических элементов на р-n-р и n-р-n транзисторах. К примеру, если в ТТЛ удалось бы заменить выходной каскад на двухтактный комплиментарный, принципиально повысилась бы экономичность элемента. Однако биполярная комплиментарная транзисторная логика не прижилась из-за трудности изготовления на кристалле большого количества компактных по площади и высококачественных по параметрам интегральных р-n-р транзисторов.

Логические элементы получались крайне медленнодействующими, из-за огромного внутреннего сопротивления канала полевого транзистора (1015 Ом), это на порядки больше чем сопротивление между коллектором и эмиттером насыщенного биполярного транзистора. Однополярные микросхемы МОП не отличались ни помехоустойчивостью, ни малой потребляемой мощностью. Хорошие результаты дало применение двух полярного инвертора, построенного на комплиментарной полевой паре.

Напомним, что в аналоговой схемотехнике, где р-n-р транзисторы просто необходимы как для упрощения схемотexники, так и для улучшения свойств усилителей, проблема создания хороших р-n-р транзисторов для технологов все еще существует. Поэтому реально биполярные микросхемы ТТЛ имеют на выходе так называемый квазикомплиментарный каскад. На кристалле делают только n-р-n транзисторы. Эта компромиссная схема элемента ТТЛ оказалась оптимальной и перспективной на многие десятилетия. Основываясь на этом, в данном проекте рассматриваются ТТЛ-схемы.

Отечественная промышленность выпускает обширную номенклатуру интегральных микросхем. Широкое применение для построения устройств автоматики и вычислительной техники находят цифровые микросхемы ТТЛ–серий – К155, К555, К531.

В данном проекте используются микросхемы серии К555 и К155. Микросхемы серии К555 были выбраны из-за малой энергетической потребности в отличии от серии К155 и К531 [2].

В качестве элемента «ИЛИ» была взята микросхема К555ЛЛ1 [2]. Микросхема содержит три элемента «ИЛИ». В качестве сумматора возьмем Сумматор К555ИМ6 [2].Так как этот сумматор подходит по серии и по параметрам самого сумматора (схема с ускоренным переносом).

В качестве элемента «регистр» введен макрос (D), который состоит из 8 D- триггеров К155ТМ2 [2].

Элементы схемы крепятся на плате, в соответствии с правилами сборки микросхем.

Непосредственно схема способна умножить 2 числа размером в байт за время равное 720нс.

2.1 Конструктивное содержание схемы.

Устройство счёта конструктивно состоит из 3х условных блоков.

Блок выдачи информации в схему предназначен для выдачи информации в схему после окончания подачи входных данных. Допускается подача входных данных заблаговременно, так как они не поступят на схему раньше, чем завершится предыдущее вычисление.

Блок выдачи результата предназначен для выдачи результата из устройства, даже во время счёта. Этот же блок занимается анализом остатка и округлением результата. В этом блоке используются сдвигающие регистры.

Блок умножения предназначен для умножения двух восьмиразрядных чисел.

2.1.1 Блок приема информации в схему и выдачи результата.

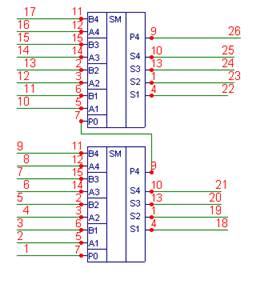

Состоит из четырех регистров (макросов D на основе D-триггеров К155ТМ2), два входных два выходных.

к входам, которых подаются данные для счёта (прямой код). При поступлении синхроимпульса происходит загрузка данных в регистры, а через 14нс, счёт.

Через 100нс синхроимпульс доходит до двух выходных регистров (старший и младший байт результата), после этого на выходах регистров находится результат.

Особенность данных регистров, что они перед началом работы должны быть очищены инверсным импульсом очистки, поданным на вход R. Т

2.1.2 Блок умножения.

Состоит из 64 логических элементов «И» объединенных в блоки по 8 (макрос Big_and), четырех сумматоров на 8 разрядов (макросы Summ1), трех сумматоров на двенадцать (макросы Summ2). Не стоит забывать, что логические элементы обладают определённым временем установления, о чём указывают производители данных микросхем. Поэтому для некоторых разрядов используются элементы задержки, которые задерживают результат на 15 нс.

Алгоритм умножения реализованный в данном проекте можно сформулировать так:

- вычисляется 8 частных произведений по 8 разрядов

- они попарно складываются, произведение, полученное от старшего разряда, сдвигается влево на 1 разряд. В результате получим 4 слова по 10 бит.

- Далее полученные слова складываются аналогично, но со сдвигом на 2 разряда. В результате получим 2 слова по 12 бит.

- Полученные слова складываются так же, но со сдвигом на 4 разряда. Полученная сумма будет искомым результатом.

При реализации этого алгоритма удается многие процессы распараллелить и таким образом решить проблему синхронизации почти полностью.

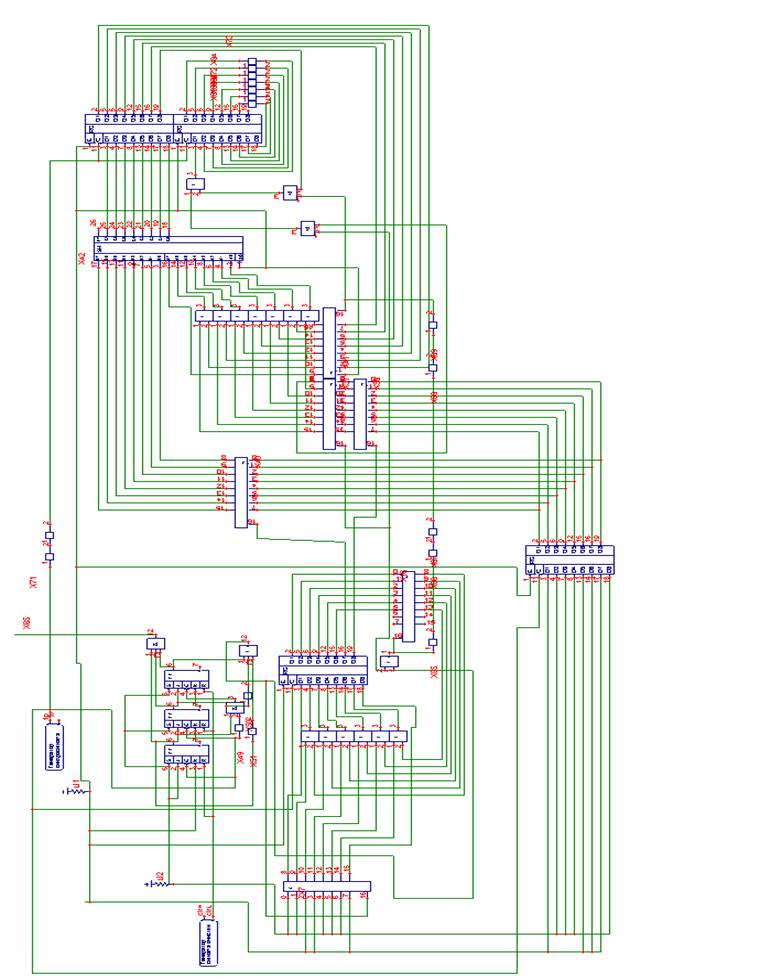

2.2 Разработка принципиальной схемы устройства.

Принципиальная схема состоит из блока выдачи информации в схему, блока выдачи результата, блока умножения. Регистры срабатывают по переднему фронту синхросигнала.

Требуется организовать связи сумматоров так, чтобы не происходило переполнения сумматоров. Необходимо синхронизировать разряды, которые поступают на вход регистра результата. Для этого использованы два элемента Пирса, оформленные в виде макроса Delta. Он имеет задержку около 20 нс, что примерно равно задержке сумматора.

Алгоритм, описанный выше, позволяет уменьшить время вычисления в лучшем случае в два раза. При реализации по стандартному методу пришлось использовать 16 четырехразрядных сумматоров. В данном проекте использовано 17 четырехразрядных сумматоров, но до результата разряд пройдет в худшем случае 8 сумматоров. Таким образом аппаратные затраты немного увеличились, но при этом быстродействие возросло в 1.6 раз. Схема работает с фиксированным временем выполнения так, что не требуется специальное устройство выдачи сигнала готовности для выдачи результата счёта и начала следующего счёта.

3. Выбор платы.

В базовой несущей конструкции блока возможно применение узлов с платами двух видов:

- многослойная печатная плата (МПП), выполненная методом открытых контактных площадок;

- двухсторонняя печатная плата (ДПП), изготовленная методом химического травления на основе фольгированного стеклотекстолита.

ДПП позволяет устанавливать элементы как со штыревым, так и с планарными выводами. Число элементов с планарными выводами не должно превышать 25 для корпуса 401.14. Максимальная высота элементов, устанавливаемых на ДПП – 9,7 мм.

Для комбинационного блока умножения выбираем плату ДПП.

Размеры платы возьмем 115x150 мм. В качестве основы возьмем стеклоткань, в качестве пропитки возьмем смолу. Медную фольгу и готовый диэлектрик затем прессуют.

При оценке качества поверхности меди, лучше всего стандарт mil p 13949d. [5].

В качестве припоя возьмем Бело-водную канифоль, у которой хорошая надежность. Марку меди возьмем 70а [5].

4.Моделирование.

Проведём моделирование в системе MICRO-CAP 5.

На входы подадим начальные значения, с выходов снимем результат.

Используем генератор строба для подачи синхроимпульсов входных и выходных регистров.

Соответственно:

Синхроимпульс имеет выражение

.define in1

+ 0ns 1

+ label=start

+ +70ns 0

+ +30ns 1

+ +70ns goto start -1 times

Сигналы генератора очистки.

.define inclear

+ 0ns 1

+ 25ns 0

.define clearbar

+ 0ns 0

+ 25ns 1.

Первые 100 нс, являются подготовительными: триггеры приводяться в рабочее положение.

Время от прихода синхросигнала на входные регистры до выдачи результаты на выходных регистрах составляет 115нс.

5. Разработка конструкции.

Создание макросов.

Макросы создаются

Для создания макроса открываем меню File, выбираем пункт New -> Schematic, нажимаем экранную кнопку OK. Появляется пустое окно, в котором необходимо нарисовать схему макроса. Затем нужно нажать на кнопку с буквой Т на панели инструментов. И на каждом информационном входе всех элементов создаем выводы, каждый из которых помечаем. После того как схема нарисована, сохраняем ее в файле с уникальным названием.

Затем в меню Windows выбираем пункт Shape Editor. Справа в дереве выбирем нужную нам группу и нажимаем кнопку ADD, вводим нужное имя (для простоты можно ввести то имя под которым сохранен макрос). В окне рисуем внешний вид макроса, затем нажимаем кнопку Close, и затем подтверждаем сохранение изменений.

Вторично выбираем меню Windows, пункт Component Editor. Нажимаем кнопку Add Component. В поле Shape выбираем имя создаваемого макроса. В поле Definition выбираем Macro. Устанавливаем галочку в поле Model = Component Name. В окне с изображением макроса наводим курсор на каждую ножку и вводим ее название в соответствии с названиями на схеме макроса. Нажимаем на кнопку Close, и подтверждаем сохранение изменений.

5.1 Спецификация макросов:

Наименование: Delta

Назначение: формирование задержки 20нс

Состав: К155ЛЕ3 - 2 эл.

Наименование: D

Назначение: восьмиразрядный регистр

Состав: К155ТМ2 - 8 эл.

Наименование: Summ1

Назначение: восьмиразрядный сумматор

Состав: К555ИМ6 – 2 эл.

Наименование: Big_And

Назначение: выполнение восьми конъюнкции с общим операндом

Состав: К155ЛИ1 - 8 эл.

5.2 Спецификация.

| Позиционное обозначение | Наименование | количество |

| DD1.1 –DD1.4 | Макрос D | |

| DD2.1 – DD2.8 | Макрос Big_And | |

| DD3.1 – DD3.4 | Макрос Summ1 | |

| DD5.1 – DD5.17 | Макрос Delta | |

| DD6.1 | Генератор тактовых импульсов | |

| DD7.1 | Генератор сигнала очистки | |

| DD8.1 | Генератор постоянных значений | |

| DD9.1 | Генератор синхросигнала |

Заключение.

В результате проделанной работы был спроектирован комбинационный восьми разрядный блок умножения. Схема работает с фиксированным временем выполнения так, что не требуется специальное устройство выдачи сигнала готовности для выдачи результата счёта и начала следующего счёта. Одновременно позволяет аппаратно привязать устройство к другому вычислителю, учитывая постоянное время счёта.

Был выбран необходимый набор элементов. Была сконструирована плата. Данная схема была смоделирована в Micro-Cap, где временными диаграммами была подтверждена правильность работы данной схемы.

Устройство нуждается во внешней синхронизации, что требуется для привязки его к другим устройствам, и возможности помещения его в ЭВМ, или, наиболее вероятно, какое-нибудь другое специализированное устройство, которому нужны функции, выполняемые устройством.

СПИСОК ИСПОЛЬЗУЕМОЙ ЛИТЕРАТУРЫ

1. Курсанов О.И.

РЕКОМЕНДАЦИИ ПО МОДЕЛИРОВАНИЮ, РАЗРАБОТКЕ

И КОНСТРУИРОВАНИЮ ЭЛЕКТРОННЫХ УЗЛОВ

2. В.Л.Шило ’’ Популярные цифровые микросхемы ‘ Справочник М.”Радио и связь” 1989г.

3. Бирюков С.А. «Цифровые устройства на МОП-интегральных микросхемах» М.: Радио и связь,1990 г.

4. Э.Т. Романычева, А.К. Иванова, А.С. Куликов и др.; Под ред. Э. Т. Романычевой. «Разработка и оформление конструкторской документации радиоэлектронной аппаратуры» справочник– 2-е изд., перераб. и доп. – М.: Радио и связь, 1989. – 448 с.: ил.

5. Файзулаева Б. Н. “Справочник по печатным платам “,” Советское радио” М, 1972г.

|

|

|

Временные диаграмы

Масштаб

Дата добавления: 2015-10-29; просмотров: 138 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| ГЛАВА ЧЕТВЕРРўРђРЇ | | | Кэш-память диска. |