|

Читайте также: |

Схема последовательного сумматора приведена на рис. 8-12а. Последовательный сумматор содержит всего один одноразрядный сумматор, выход переноса Р1 которого соединен со входом Р0 через D -триггер. Изображенные на схеме регистры RG не входят в схему последовательного сумматора. Они служат для подачи на вход сумматора разрядов слагаемых (регистры 1 и 2) и приема разрядов суммы с выхода сумматора (регистр 3).

а)

б)

Рис. 8-12

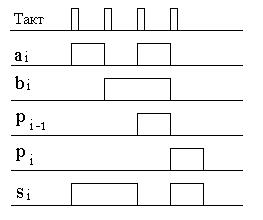

Операция суммирования во всех разрядах слагаемых осуществляется с помощью одного и того же одноразрядного сумматора, обрабатывающего последовательно разряд за разрядом, начиная с младшего. Сложив младшие разряды, одноразрядный сумматор вырабатывает сумму для младшего разряда результата и перенос, который запоминается на один такт в триггере. В следующем такте складываются вновь поступившие разряды слагаемых ai и bi с переносом из младшего разряда и т. д. На рис. 8- 11 показана временная диаграмма, соответствующая операции сложения двух чисел 101 + 110= 1011 или в десятичном выражении 5 + 6 = 11.

Дата добавления: 2015-07-21; просмотров: 78 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Двоичные сумматоры | | | Параллельные сумматоры |