|

Читайте также: |

Сложнее обстоит дело с возможностью программирования FLASH ПЗУ под управлением прикладной программы. Даже если модуль FLASH ПЗУ содержит встроенный генератор накачки, то попытка перевода модуля в режим программирования посредством установки битов режима приведет к невозможности дальнейшего считывания программы, которая в это FLASH ПЗУ записана. И МК "зависнет". Поэтому та часть программы, которая реализует программирование FLASH ПЗУ, должна быть обязательно расположена в памяти другого типа. Наиболее часто в качестве такой памяти выбирают ОЗУ МК. Поскольку, если в МК имеется EEPROM ПЗУ, то бессмысленно "допрограммировать" FLASH в процессе работы изделия, в противном случае другой памяти, кроме ОЗУ, в МК просто нет. Если МК допускает возможность выполнения программы, расположенной в ОЗУ, и имеет встроенный генератор накачки модуля FLASH ПЗУ, то такой МК становится "программируемым в системе" ("In system programmable"). Для того чтобы возможность программирования в системе стала реализуемой, необходимо предусмотреть пути, по которым в ОЗУ МК будет передана программа алгоритма программирования FLASH ПЗУ, а затем порциями будут передаваться коды прикладной программы, которая должна быть занесена во FLASH ПЗУ. Не следует забывать, что объем сегмента программирования значительно превышает объем резидентного ОЗУ МК. В качестве такого пути разработчики МК назначают один из последовательных портов МК. Обслуживание порта реализует специальная программа монитора связи, которая расположена в резидентном масочном ПЗУ МК. Эта программа активизируется посредством установки определенных линий ввода/вывода МК в указанное в спецификации состояние при сбросе МК или простым обращением к ней. Способ активизации указан в техническом описании МК. По последовательному интерфейсу связи персональный компьютер загружает в ОЗУ МК сначала коды программы программирования, а затем порциями коды прикладной программы для программирования. Возможны также решения, при которых программа программирования сразу записана в память масочного типа и не требует загрузки в ОЗУ МК.

Рассмотренный режим программирования в системе в настоящее время все шире используется для занесения прикладной программы в МК, расположенный на плате конечного изделия. Специальный программатор в этом случае не нужен. Кроме того, надежность программирования гарантируется внутренними режимами МК и не зависит от схемных решений программатора. Однако режим программирования в системе отличается от режима "допрограммирования" нескольких байтов FLASH-памяти под управлением прикладной программы в процессе работы системы. Теоретически возможно решение, при котором программа программирования, хранящаяся во FLASH ПЗУ, сначала будет перенесена в ОЗУ под управлением прикладной программы, а затем выполнена из ОЗУ. Но при таком решении на время программирования потребуется запретить все прерывания МК, поскольку их обслуживание невозможно по причине недоступности векторов прерывания. Поэтому реализация описанного режима возможна далеко не всегда. В качестве одного из путей предлагается разбить модуль FLASH ПЗУ на два, с независимыми генераторами накачки и регистрами управления. Таков решение предложено в МК HC908AZ60 фирмы Motorola. Тогда один из модулей может быть поставлен в режим программирования, в то время как программа программирования будет выполняться из другого модуля. Впрочем, следует надеяться, что в недалеком будущем проблема программирования FLASH-памяти программой из FLASH-памяти будет решена. А пока наиболее совершенные модели МК со свойством программирования в системе часто имеют в своем составе четыре типа памяти: FLASH ПЗУ программ, масочное ПЗУ монитора связи, EEPROM ПЗУ для хранения изменяемых констант и ОЗУ промежуточных данных.

Технология создания резидентной FLASH-памяти МК непрерывно совершенствуется. Одни из лучших показателей достигнуты в МК семейства HC08 фирмы Motorola:

* Гарантированное число циклов стирания/программирования составляет 105.

* Гарантированный период хранения записанной информации равен 10 годам, т.е. составляет жизненный цикл изделия.

* Модули FLASH-памяти работают и программируются при напряжении питания МК от 1.8 до 2.7 В.

* Эквивалентное время программирования одного байта памяти снижено до 60 мкс, что позволяет выполнить программирование МК с 32 КБайт памяти в течение 2 с. Перспективные технологии FLASH-памяти предполагают увеличение скорости программирования до 1 Мбит/с.

Кроме ПЗУ, в состав МК входит также истатическое оперативное запоминающее устройство. Определение "статическое" выделено не случайно: современные 8-разрядные МК допускают снижение частоты тактирования до сколь угодно малых значений с целью снижения энергии потребления (см. п. 1.1.9). Содержимое ячеек ОЗУ при этом сохраняется, в отличие от динамической памяти. В качестве еще одной особенности следует отметить, что большинство МК в техническом описании имеет параметр "напряжение хранения информации" — Ustandby. При снижении напряжения питания ниже минимально допустимого уровня Uddmin, но выше напряжения хранения Ustandby программа управления микроконтроллером выполняться не будет, но информация в ОЗУ сохранится. Тогда при восстановлении напряжения питания можно будет выполнить сброс МК и продолжить выполнение программы без потери данных. Уровень напряжения хранения составляет примерно 1В. Это позволяет в случае необходимости перевести МК на питание от автономного источника (батареи или аккумулятора) и сохранить тем самым данные ОЗУ. Большого расхода энергии потребления в этом случае не будет, т.к. система тактирования МК может быть отключена. (В последнее время появились МК, которые в корпусе имеют автономный источник питания, гарантирующий сохранение данных в ОЗУ на протяжении 10 лет (МК DS5000 фирмы Dallas Semiconductor).

4. ПОРТЫ ВВОДА/ВЫВОДА

Каждый МК имеет некоторое количество линий ввода/вывода, которые объединены в 8-разрядные параллельные порты ввода/вывода РТx ("х" — имя порта, используемое в техническом описании). В карте памяти МК каждый порт ввода/вывода представлен регистром данных порта DPTx. В режиме ввода логические уровни сигналов на линиях порта РТх отображаются нулями и единицами в соответствующих разрядах регистра DPTx. В режиме вывода данные, записанные под управлением программы в регистр DPTx, передаются на выводы МК, которые отмечены в качестве линий порта РТх. Обращение к регистру данных DPTx осуществляется теми же командами, что и обращение к ячейкам оперативной памяти. Кроме того, во многих МК отдельные разряды портов могут быть опрошены командами битового процессора.

В зависимости от функций, которые реализуют те или иные порты ввода/вывода, различают следующие типы параллельных портов:

1. Однонаправленные порты, предназначенные в соответствии со спецификацией МК только для ввода или только для вывода информации.

2. Двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации системы.

3. Порты с альтернативной функцией. Отдельные линии этих портов связаны со встроенными в МК периферийными устройствами, такими, как таймер, АЦП, контроллеры последовательных приемопередатчиков. Если соответствующий периферийный модуль МК не используется, то его выводы можно задействовать как обычные линии ввода/вывода. Напротив, если модуль активизирован, то принадлежащие ему линии ввода/вывода автоматически конфигурируются в соответствии с функциональным назначением в модуле и не могут быть использованы в качестве линий ввода/вывода.

4. Порты с изменяемой программно управляемой схемотехникой входного буфера.

По сути, порты служат в качестве устройства согласования масштабов времени, в которых функционируют объект управления и ядро МК, производящее обработку информации. Объект управления и МП-система на основе МК асинхронны друг по отношению к другу. Для качественного управления информация с датчиков состояния объекта должна быть получена в моменты времени, определяемые поведением объекта. Однако не всегда именно в эти моменты времени информация может быть воспринята МП-системой. В этом случае порты ввода/вывода выполняют функцию накопителя, который запоминает состояние объекта в один момент времени и передает его в процессор в другой момент времени. Различают три типа алгоритмов обмена между МК и внешним устройством через параллельные порты ввода/вывода:

1. Режим простого программного ввода/вывода.

2. Режим ввода/вывода со стробированием.

3. Режим ввода/вывода с полным набором сигналов квитирования.

3. Режим ввода/вывода с полным набором сигналов квитирования.

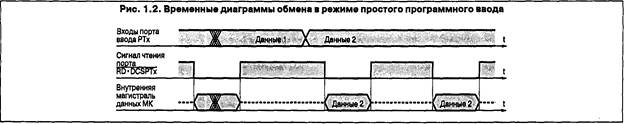

Временные диаграммы простого программного ввода представлены наРис. 1.2. Внешнее устройство изменяет данные на линиях порта РТх в произвольный момент времени. Событие обновления кода и момент его наступления не отмечаются дополнительными сигналами. Информация об изменении кода на линиях порта ввода в МК не передается. МК производит считывание данных с порта РТх в моменты времени, которые определяются только ходом вычислительного процесса и не связаны с моментами изменения данных на линиях порта РТх. Поэтому одно и то же состояние линий порта РТх может быть считано несколько раз подряд, но может быть и пропущено, если данные на линиях порта изменяются слишком часто. При обращении к регистру данных порта DPTx МК формирует сигнал чтения и состояние линий РТх7...РТхО по внутренней магистрали данных передается в один из регистров центрального процессора. Если состояние линий порта РТх7...РТхО в этот момент изменяется, то считанные данные могут оказаться ошибочными. В случае изменения состояния только одной линии в регистре CPU будет зафиксировано предшествующее, или последующее значение, но оба эти значения будут достоверными, В случае изменения состояния сразу нескольких линий может возникнуть классическая ситуация гонок в цифровой системе, и прочитанное слово окажется недостоверным.

Временные диаграммы простого программного ввода представлены наРис. 1.2. Внешнее устройство изменяет данные на линиях порта РТх в произвольный момент времени. Событие обновления кода и момент его наступления не отмечаются дополнительными сигналами. Информация об изменении кода на линиях порта ввода в МК не передается. МК производит считывание данных с порта РТх в моменты времени, которые определяются только ходом вычислительного процесса и не связаны с моментами изменения данных на линиях порта РТх. Поэтому одно и то же состояние линий порта РТх может быть считано несколько раз подряд, но может быть и пропущено, если данные на линиях порта изменяются слишком часто. При обращении к регистру данных порта DPTx МК формирует сигнал чтения и состояние линий РТх7...РТхО по внутренней магистрали данных передается в один из регистров центрального процессора. Если состояние линий порта РТх7...РТхО в этот момент изменяется, то считанные данные могут оказаться ошибочными. В случае изменения состояния только одной линии в регистре CPU будет зафиксировано предшествующее, или последующее значение, но оба эти значения будут достоверными, В случае изменения состояния сразу нескольких линий может возникнуть классическая ситуация гонок в цифровой системе, и прочитанное слово окажется недостоверным.

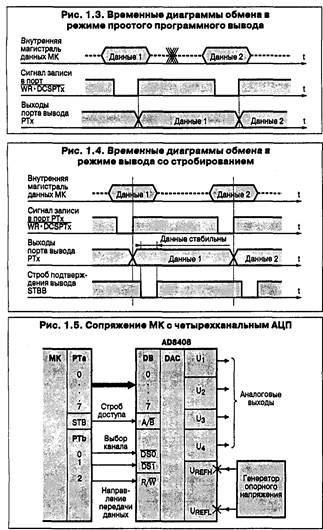

В режиме простого программного вывода (Рис.1.3) состояние линий порта РТх7...РТхО изменяется после каждой операции записи в регистр данных DPTx. Это состояние сохраняется неизменным до тех пор, пока МК не запишет новые данные в регистр DPTx.Возможность передачи недостоверной информации устраняет режим стробируемого ввода/вывода. При выводе данных в этом режиме (Рис. 1.4) каждое изменение данных на линиях порта сопровождается коротким стробом подтверждения вывода STBB (обычно 1...2 периода fbus МК). Этот строб может быть использован для записи данных в регистр периферийной ИС. Например, наРис. 1.5 показан вариант использования режима стробируемого вывода для передачи информации в четырехканальный ЦАП AD8408 фирмы Analog Devises. Микросхема AD8408 имеет 8-разрядную магистраль данных и два входа встроенного дешифратора адресации канала ЦАП, в регистр которого производится запись. Магистраль данных ЦАП соединена с линиями порта РТа, который работает в режиме стробируемого вывода. Две линии порта РТb используются для задания номера канала ЦАП. Порт РТb работает в режиме  простого программного вывода.

простого программного вывода.

Режим ввода данных со стробированием (Рис. 1.6) позволяет избежать считывания недостоверной информации в случае, если момент чтения совпадает с моментом изменения многоразрядного кода на входе. В этом режиме для обслуживания порта ввода/вывода используется дополнительный регистр-защелка DPTLx, в котором запоминаются данные, присутствующие на входе порта во время строба. При работе в режиме стробируемого ввода линии порта могут быть использованы как для контроля за текущим состоянием (тогда данные следует читать из регистра DPTx), так и для ввода стробируемой информации (тогда данные следует читать из регистра-защелки DPTLx).

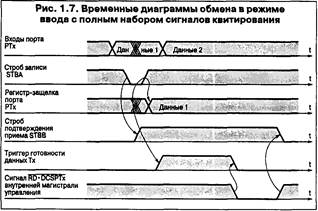

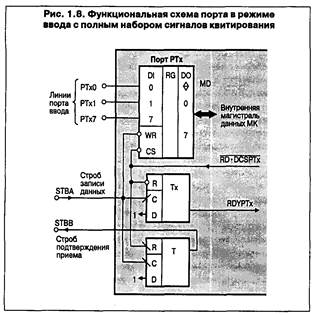

Режим обмена с полным набором сигналов квитирования наиболее часто используется для обмена в параллельном коде между двумя МК. НаРис. 1.7 и 1.8 представлены временные диаграммы работы и функциональная модель порта ввода данных в рассматриваемом режиме. Каждое изменение данных на линиях порта РТх внешнее устройство сопровождает импульсом записи на линии STBA. Данные с входов порта РТх передаются в триггеры регистра DPTLx при низком активном уровне STBA. По положительному фронту сигнала STBA эти данные запоминаются в регистре-защелке порта DPTLx. Одновременно аппаратными средствами формируется нарастающий фронт сигнала подтверждения приема STBB. Высокий логический уровень STBB  информирует внешнее передающее устройство о том, что данные в регистр-защелку помещены, но еще не считаны в память МК. Поэтому передавать новые данные не следует. Высокий активный уровень сигнала STBB устанавливается именно по срезу сигнала STBA: передаваемые данные еще не запомнены в DPTLx, но передача начата и, следовательно, приемное устройство уже занято. По положительному фронту сигнала STBA передаваемые данные запоминаются. Следовательно, изменения данных уже не будет и аппаратные средства устанавливают в 1 триггер готовности данных Тх. Этот триггер может быть считан под управлением программы, он отображается в одном из регистров специальных функций МК. Путем инициализации можно также назначить прерывания по триггеру готовности данных. По состоянию триггера готовности данных МК обнаруживает, что в регистре-защелке порта DPTLx находятся данные, и производит считывание.

информирует внешнее передающее устройство о том, что данные в регистр-защелку помещены, но еще не считаны в память МК. Поэтому передавать новые данные не следует. Высокий активный уровень сигнала STBB устанавливается именно по срезу сигнала STBA: передаваемые данные еще не запомнены в DPTLx, но передача начата и, следовательно, приемное устройство уже занято. По положительному фронту сигнала STBA передаваемые данные запоминаются. Следовательно, изменения данных уже не будет и аппаратные средства устанавливают в 1 триггер готовности данных Тх. Этот триггер может быть считан под управлением программы, он отображается в одном из регистров специальных функций МК. Путем инициализации можно также назначить прерывания по триггеру готовности данных. По состоянию триггера готовности данных МК обнаруживает, что в регистре-защелке порта DPTLx находятся данные, и производит считывание.  В процессе чтения формируется сигнал выборки регистра-защелки RD • DCSPTLx, отрицательный фронт которого сбрасывает триггер готовности Тх. Позднее по нулевому состоянию триггера готовности Тх МК сможет определить, что предыдущие данные уже считаны из порта, а новые еще не поступили. Положительный фронт сигнала

В процессе чтения формируется сигнал выборки регистра-защелки RD • DCSPTLx, отрицательный фронт которого сбрасывает триггер готовности Тх. Позднее по нулевому состоянию триггера готовности Тх МК сможет определить, что предыдущие данные уже считаны из порта, а новые еще не поступили. Положительный фронт сигнала  выборки устанавливает в 0 линию подтверждения приема STBB, информируя передающее устройство, что данные прочитаны микроконтроллером из порта в память, и можно передавать новые.

выборки устанавливает в 0 линию подтверждения приема STBB, информируя передающее устройство, что данные прочитаны микроконтроллером из порта в память, и можно передавать новые.

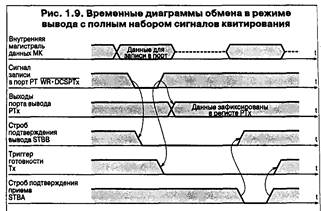

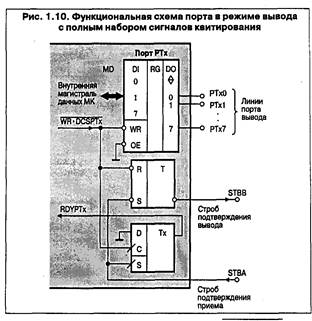

Временные диаграммы вывода с полным набором сигналов квитирования представлены наРис. 1.9, Рис. 1.10 отражает функциональную модель порта. МК записывает данные в регистр данных порта РТх под управлением программы. При этом формируется внутренний сигнал записи WR • DCSPTx, отрицательный фронт которого устанавливает в 0 сигнал подтверждения вывода STBB для принимающего устройства. По положительному фронту WR • DCSPTx сбрасывается триггер Тх. В этом режиме его можно интерпретировать как триггер готовности порта к обмену. Нулевое состояние триггера Тх информирует МК о том, что данные, ранее записанные в порт, еще не считаны внешним устройством. Принимающее устройство считывает данные с линий порта РТх, копируя их в одном из собственных регистров, и формирует строб подтверждения приема STBA. В ответ передающее устройство устанавливает в 1 сигнал подтверждения вывода STBB. Наличие высокого логического уровня на этой линии свидетельствует об отсутствии новых данных на линиях порта вывода. По положительному фронту сигнала STBA устанавливается в 1 триггер готовности порта к обмену, информируя МК о том, что предыдущие данные приняты внешним устройством и можно записать в порт новые. Аналогично предыдущему случаю, состояние триггера готовности порта к обмену Тх может быть считано программно или генерируется запрос на прерывание.

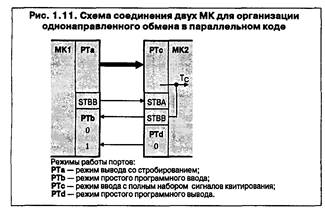

Рассмотрим использование режимов обмена с полным набором сигналов квитирования на примере передачи массива данных в параллельном коде между двумя МК. Структурная схема связи МК приведена наРис. 1.11. Передача массива происходит из МК1 в МК2. Передачу инициирует МК1. Формат передаваемого массива следующий: <число элементов массива n>, Олемент 1>, Олемент 2>,... <элемент n>, <контрольная сумма>. Адрес размещения массива в памяти МК2 определен заранее.

1. МК1 анализирует состояние линии STBB. Если 0, то порт РТс МК2 свободен для приема данных от МК1.

2. МК1 производит запись числа элементов передаваемого массива (первый байт посылки) в порт РТа. Одновременно аппаратными средствами формируется строб записи STBA.

2. МК1 производит запись числа элементов передаваемого массива (первый байт посылки) в порт РТа. Одновременно аппаратными средствами формируется строб записи STBA.

3. MK2 запоминает данные в регистре-защелке DPTLc и одновременно выставляет в 1 триггер готовности данных Тc. Сигнал с выхода триггера Те поступает в подсистему прерывания МК2. МК2 переходит на выполнение подпрограммы прерывания, в которой инициализирует начальный адрес области записи принимаемого массива, запрещает прерывания по триггеру готовности данных Тc, считывает содержимое порта РТс в память, устанавливая таким образом начальное значение счетчика циклов обмена. В процессе чтения РТс триггер Тс сбрасывается и линия подтверждения приема данных STBB устанавливается в 0.

4. МК1 после выдачи первого байта переходит к опросу линии STBB. При установке линии в 0 происходит запись очередного байта в регистр порта РТа. Автоматически формируется очередной строб записи STBA.

5. МК2 принимает все байты, кроме первого, путем программного опроса триггера готовности Тс. После завершения приема байта с номером n MK2 вычисляет контрольную сумму принятого массива и принимает последний байт от МК1. MK2 производит сравнение рассчитанной и принятой контрольной суммы. В случае их равенства устанавливает в 1 бит PTd0. MK2 завершает обмен, разрешая прерывания по триггеру Тс.

6. МК1 после передачи байта контрольной суммы формирует задержку времени, необходимую MK2 для сравнения контрольных сумм. Далее считывает РТЫ и выходит из подпрограммы обмена. Если равенство контрольных сумм не установлено, то подпрограмма обмена может быть повторена.

Приведенный алгоритм не учитывает возможности "зависания" одного из МК, которое может произойти, например, из-за обслуживания прерывания более высокого уровня. Для того чтобы другой МК не находился в состоянии долгого ожидания сигнала подтверждения приема (МК1) или готовности данных (MK2), следует при анализе каждого из этих битов запускать таймер, а при выполнении условия обработки следующего байта этот таймер сбрасывать. Тогда, если условие приема или передачи следующего байта не наступило в течение отведенного времени, то таймер переполняется и прерывает программу обмена.

В ряде МК реализуется модификация режима вывода с полным набором сигналов квитирования, при которой буферы порта вывода становятся активными только во время формирования строба подтверждения приема информации. Это удобно с точки зрения уменьшения энергии потребления, т.к. буферы порта большую часть времени во время обмена находятся в высокоумном состоянии и практически не потребляют ток. Обычно активные уровни сигналов квитирования обмена STBA и STBB настраиваются программно посредством установки битов регистра управления режимами порта РТСх (Табл.1.2).

Если в составе МК нет порта, который поддерживает стробируемый обмен или обмен с сигналами квитирования, то эти алгоритмы могут быть воспроизведены программным способом.

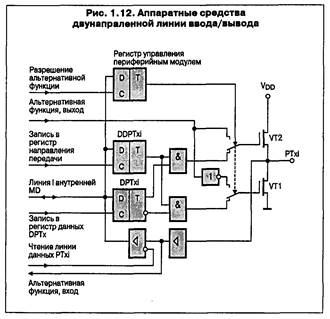

Перейдем к рассмотрению схемотехнических особенностей буферов линий ввода/вывода МК. Во-первых, следует отметить, что во всех современных МК двунаправленные порты ввода/вывода выполнены с возможностью независимого задания направления передачи каждой линии. Т.е. объединение групп линий в порты позволяет организовать обращение к ним как к ячейкам памяти, что удобно при организации обмена в параллельном формате. Но в случае необходимости каждая линия может быть сконфигурирована индивидуально и обслужена командами битового процессора, независимо от других линий того же порта ввода/вывода. Учитывая это обстоятельство, схемотехника портов ввода/вывода рассматривается на уровне одной линии.

Различают три типа драйверов ввода/вывода:

* Двунаправленные линии, которые настраиваются на ввод или на вывод программированием бита в регистре направления передачи DDPTx.

* Квазидвунаправленные линии, которые не требуют предварительной инициализации, но имеют некоторые особенности при считывании.

* Двунаправленные линии с возможностью программного подключения "подтягивающих" резисторов.

Примером драйверов первого типа могут служить драйверы линий ввода/вывода МК НС05 и НС08 фирмы Motorola(Рис. 1.12). Каждой линии порта поставлен в соответствие одноименный разряд регистра направления передачи DDPTx. Нулевое значение разряда конфигурирует линию на ввод, единичное — на вывод. После сброса МК все линии настроены на ввод. Из Рис. 1.12 видно, что в режиме ввода непосредственно в момент считывания логический уровень сигнала линии PTxi передается на внутреннюю магистраль данных, минуя регистр данных порта DPTx. В процессе чтения состояние линии не запоминается в регистре DPTx, и, следовательно, каждое новое обращение к порту ввода может возвращать новое значение. В режиме ввода транзисторы VT1 и VT2 закрыты, буфер находится в высокоомном состоянии (Z-состояние). Возможна ситуация, при которой операция чтения неподключенного входа будет возвращать нулевое значение. Поэтому, если в качестве источника сигнала используется открытый коллекторный выход или релейный контакт (Рис. 1.12), то уровень сигнала при разомкнутом контакте в общем случае не определен. Для задания единичного логического уровня сигнала при разомкнутом контакте следует подключить внешний резистор, который обычно обозначают Rpullup. В режиме вывода транзисторы VT1 и VT2 управляются сигналом с выхода триггера регистра данных DPTx.

Примером квазидвунаправленных драйверов портов могут служить порты МК Intel MCS-51(Рис.1.13). Особенность этих драйверов заключается в том, что при считывании возвращаемое значение равно логическому произведению сигнала на линии и содержимого одноименного триггера регистра данных порта DPTx. По этой причине те разряды порта, которые будут считываться, должны быть предварительно установлены в 1 командой записи в порт и лишь затем прочитаны.

Примером квазидвунаправленных драйверов портов могут служить порты МК Intel MCS-51(Рис.1.13). Особенность этих драйверов заключается в том, что при считывании возвращаемое значение равно логическому произведению сигнала на линии и содержимого одноименного триггера регистра данных порта DPTx. По этой причине те разряды порта, которые будут считываться, должны быть предварительно установлены в 1 командой записи в порт и лишь затем прочитаны.

Квазидвунаправленные порты не имеют регистра направления передачи и, следовательно, не должны инициализироваться. Кроме того, драйвер линии портов этого типа содержит "подтягивающий" резистор Rpullup поэтому операция чтения разомкнутого контакта будет возвращать 1.

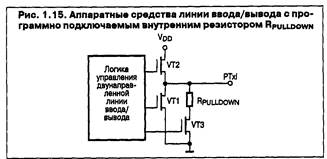

Драйверы линий с изменяемой схемотехникой могут быть выполнены двумя способами (Рис.1.14 и 1.15). Однако преследуемая цель одна — сократить число навесных элементов платы МП контроллера. В первом случае (Рис. 1.14) драйвер каждой линии содержит "подтягивающий к 1" резистор (Rpullup), который обеспечивает уровень логической единицы на входе при разомкнутом контакте. Во втором случае (Рис. 1.15) драйвер дополнен "подтягивающим к 0" резистором (Rpulldown). который способен служить нагрузочным резистором датчика, выходной каскад которого выполнен по схеме эмиттерного повторителя. Логика управления встроенными "подтягивающими" резисторами одинакова для обоих типов драйверов:

Драйверы линий с изменяемой схемотехникой могут быть выполнены двумя способами (Рис.1.14 и 1.15). Однако преследуемая цель одна — сократить число навесных элементов платы МП контроллера. В первом случае (Рис. 1.14) драйвер каждой линии содержит "подтягивающий к 1" резистор (Rpullup), который обеспечивает уровень логической единицы на входе при разомкнутом контакте. Во втором случае (Рис. 1.15) драйвер дополнен "подтягивающим к 0" резистором (Rpulldown). который способен служить нагрузочным резистором датчика, выходной каскад которого выполнен по схеме эмиттерного повторителя. Логика управления встроенными "подтягивающими" резисторами одинакова для обоих типов драйверов:

* Подключение "подтягивающих" резисторов допускается аппаратными средствами драйвера только при конфигурировании линии порта на ввод.

* Специальный бит регистра конфигурации МК разрешает программное подключение "подтягивающих" резисторов на всех линиях ввода одновременно, но не выполняет это подключение.

* Коммутацией "подтягивающего" резистора каждой линии управляет одноименный бит регистра входного сопротивления PTUEx. Значение этого бита может многократно изменяться в ходе выполнения прикладной программы, тем самым осуществляется динамическое управления входным сопротивлением линии порта ввода и током потребления этой линии. Обычно в методических указаниях не рекомендуется оставлять линии не подсоединенными к источнику сигнала. В этом случае снижается помехозащищенность. Поэтому, если датчик представляет собой релейный нормально разомкнутый контакт, то не следует отключать резистор Rpullup на время, когда состояние датчика не опрашивается. Напротив, если используется релейный датчик с нормально замкнутым контактом, то с целью снижения потребляемого тока "подтягивающий" резистор Rpullup следует коммутировать только на время опроса.

Табл. 1.2 Регистры управления портами ввода/вывода

| Функция порта ввода/вывода | Регистр данных DРТx | Регистр направления передачи DDPTx | Регистр-защелка DPTLx | Регистр выходного сопротивления PTUEx | Регистр управления режимом порта РТСх | Регистр конфигурации МК | Регистр управления модулем альтернативной функции |

| Однонаправленный порт | V | ||||||

| Двунаправлен-ный порт | V | V | |||||

| Порт с режимом обмена со стробированием | V | V | V | V | |||

| Порт с изменяемым входным ссссссиротивлениемсопртивленикмсопротивлением | V | V | V | V | |||

| Порт с альтернативной функцией | V | V | V |

Рассматривая особенности драйверов линий ввода/вывода, нельзя не остановиться на понятии нагрузочной способности линии. Различают линии с нормальной и повышенной нагрузочной способностью. Если речь идет о нормальной нагрузочной способности, то следует ориентироваться на следующие цифры: I 0вых = 1.6...2.0 мА, I 1вых = 0.4...2.0 мА. Типовые значения повышенной нагрузочной способности: I 0вых = I 1вых = 25 мА, Предельное значение повышенной нагрузочной способности на сегодняшний день составляет I 1вых = 60 мА для Microchip PIC17. Следует заметить, что число выводов с повышенной нагрузочной способностью обычно ограничено. Кроме того, в справочных данных указан максимальный суммарный ток всех линий ввода/вывода, который ограничен теплоотводом корпуса МК.

5. ТАЙМЕРЫ И ПРОЦЕССОРЫ СОБЫТИЙ

Большинство задач управления, которые возлагаются на МП-системы, должны выполняться в реальном времени. Понятие"управление в реальном времени" означает способность МП-системы получить информацию о состоянии управляемого объекта, выполнить необходимые расчеты и сформировать управляющие воздействия в течение интервала времени, по истечении которого эти воздействия вызовут желаемое изменение поведения объекта. Возможность использования того или иного МК для управления конкретным устройством в реальном времени определяется в первую очередь производительностью процессорного ядра, т.к. МК должен успеть за строго ограниченное время выполнить расчет корректирующего воздействия. Однако только высокой производительности недостаточно. Необходимо организовать прием информации с датчиков и выдачу управляющих сигналов таким образом, чтобы при сохранении требуемой точности на эти операции расходовалось как можно меньше времени. В противном случае не останется времени для выполнения вычислений. Эффективное распределение задач управления между различными модулями МК обеспечивает возможность качественного управления в реальном времени. Многие подсистемы МК используются для решения этих задач, но в первую очередь среди них выделяютподсистему прерываний и модули таймера. Развитая подсистема прерываний позволяет сократить время реакции МП-системы на изменения состояния объекта. Модули таймеров служат для приема информации отдатчиков с времяимпульсными выходами, а также для формирования управляющих воздействий в виде последовательности импульсов с изменяющимися параметрами.

Опыт построения МП-систем позволяет выделить типовые задачи, которые должен уметь решать МК для эффективного управления в реальном времени:

* Отсчет равных интервалов времени заданной длительности, повтор алгоритма управления по истечении каждого такого временного интервала. Обычно эту функцию называют формированием меток реального времени.

* Контроль за изменением состояния линии ввода МК. * Измерение длительности сигнала заданного логического уровня на линии ввода МК.

* Подсчет числа импульсов внешнего сигнала на заданном временном интервале.

* Формирование на линии вывода МК сигнала заданного логического уровня с программируемой задержкой по отношению к изменению сигнала на линии ввода.

* Формирование на линии вывода МК импульсного сигнала с программируемой частотой и программируемым коэффициентом заполнения,

Дата добавления: 2015-07-25; просмотров: 77 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Аннотация 1 страница | | | Аннотация 3 страница |