|

Читайте также: |

Московский Государственный Горный Университет

Микроконтроллеры для встраиваемых приложений

Москва 2009

Аннотация

В учебном пособии приводится сравнительный анализ 8-ми разрядных микроконтроллеров фирм Motorola, Intel, Atmel, Philips, Microchip, Infenion. Приведены функциональные схемы основных блоков, различные электрические параметры микроконтроллеров семейств MSC-51 Intel, HC05, HC08 Motorola, PIC16, PIC17, Microchip.

Содержание

Введение ………………………………………………………………...4

1. Модульный принцип построения МК................................................6

2. Процессорное ядро МК ……………………………………………..8

3. Резидентная память МК ……………………………………………11

4. Порты ввода/вывода ………………………………………………..17

5. Таймеры и процессоры событий …………………………………..26

6. Аналогово-цифровые и цифро-аналоговые преобразователи ……37

7. Контроллеры последовательного порта …………………………...41

8. Минимизация потребления энергии в системах МК ……………..47

9. Мониторинг напряжения питания МК …………………………….53

10. Аппаратные и программные решения по повышению надежности работы МК ………………………………………………………………….56

Введение

Средства вычислительной техники, используемые для целей автоматизации управления, развиваются по двум взаимодополняющим направлениям:

1. Совершенствование архитектуры (внутренней организации), позволяющее на каждом новом витке сложности алгоритмов управления обеспечить адекватную производительность вычислительных средств.

2. Снижение уровня энергопотребления и повышение уровня надежности, которые делают функционально совершенные средства управления не только технически реализуемыми, но и целесообразными с потребительской и экономической точки зрения.

Приведем два примера. Постоянно возрастающие требования к качеству регулирования в электроприводе заставили разработчиков обратить внимание на уже использовавшиеся в других областях высокопроизводительные процессоры цифровой обработки сигналов. Но их массовое внедрение в регулируемый электропривод началось лишь тогда, когда появились специализированные однокристальные микроконтроллеры с процессором цифровой обработки сигналов в качестве вычислительного ядра. А для переносных пультов управления бытовой аппаратуры было достаточно быстродействия даже самых первых микропроцессоров. Однако пульты появились, когда энергия потребления микропроцессоров уменьшилась настолько, что стало возможным их питание от батареек.

Анализируя пути совершенствования микропроцессорных средств управления, будь то микропроцессорная элементная база для встраиваемых систем (сначала микропроцессорные комплекты ИС, а затем однокристальные микроконтроллеры) или средства промышленной автоматизации — программируемые логические контроллеры (ПЛК/PLC) и универсальные микропроцессорные комплексы, — можно заметить, что развитие их архитектуры подобно спирали с двумя ярко выраженными полюсами на каждом витке:

* На первой стадии (один полюс) производительность процессорного ядра не только достаточна, но даже превышает требования алгоритмов управления, для которых она предназначена. Поэтому многие задачи могут быть решены чисто программными средствами. Структура периферийных устройств на этом этапе еще далека от оптимальной.

* На следующем этапе (второй полюс) сохранившаяся производительность процессорного ядра становится минимально достаточной. Совершенствование структуры периферийных модулей позволяет разгрузить процессорное ядро от несвойственных ему операций.

Когда все возможности по оптимизации структуры периферии исчерпываются, начинается новый виток развития, отмеченный скачкообразным увеличением производительности процессорного ядра.

Так было при переходе от 8-разрядных микроконтроллеров к 16- и 32-разрядным: увеличение разрядности обрабатываемого слова даже при неизменной частоте тактирования существенно увеличивает производительность. Затем появились процессоры цифровой обработки сигналов (DSP). И каждый раз новый уровень производительности процессорного ядра сопровождался совершенствованием структуры периферийных устройств.

Однако увеличение производительности центрального процессора не обязательно связано с увеличением разрядности обрабатываемого слова. Это в полной мере справедливо для алгоритмов с большим объемом вычислительных операций. А для алгоритмов с преобладанием логических операций увеличение разрядности обрабатываемого слова практически не сказывается на производительности. Это обстоятельство является главной причиной жизнеспособности 8-разрядных микропроцессоров.

Элементная база 8-разрядных микропроцессоров (МП) не стоит на месте. Она уже совершила два витка в своем развитии. Первый из них приходится на МП комплекты ИС и первые однокристальные микроконтроллеры (МК). Второй, отмеченный повышением практически на порядок производительности 8-разрядного процессорного ядра и превращением в автономные модули периферийных устройств, завершается в настоящее время. И уже появились первые ласточки следующего витка спирали. Это RISC МК Scenix с частотой тактирования до 50 МГц. Пока эти МК не имеют встроенных периферийных модулей, все функции периферии эмулируются программными средствами. Надолго ли достигнутое быстродействие будет достаточно большим, чтобы обходиться без аппаратных средств?

1. МОДУЛЬНЫЙ ПРИНЦИП ПОСТРОЕНИЯ МК

МК представляют собой законченную МП-систему обработки информации, которая реализована в виде одной большой интегральной микросхемы. МК объединяет в пределах одного полупроводникового кристалла основные функциональные блоки МП управляющей системы: центральный процессор, постоянное запоминающее устройство (ПЗУ), оперативное запоминающее устройство (ОЗУ), периферийные устройства для ввода и вывода информации.

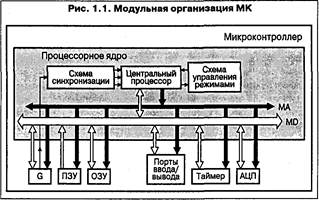

Широкое разнообразие моделей МК, возможность разработки и производства новых моделей в короткие сроки обеспечиваетмодульный принцип построения МК, который взят на вооружение всеми ведущими компаниями. При модульном принципе построения все МК одного семейства содержат в себе базовый функциональный блок, который одинаков для всех МК семейства, и изменяемый функциональный блок, который отличает МК разных моделей в пределах одного семейства (Рис.1.1)

Широкое разнообразие моделей МК, возможность разработки и производства новых моделей в короткие сроки обеспечиваетмодульный принцип построения МК, который взят на вооружение всеми ведущими компаниями. При модульном принципе построения все МК одного семейства содержат в себе базовый функциональный блок, который одинаков для всех МК семейства, и изменяемый функциональный блок, который отличает МК разных моделей в пределах одного семейства (Рис.1.1)

Базовый функциональный блок включает:

* Центральный процессор.

* Внутренние магистрали адреса, данных и управления.

* Схему формирования многофазной импульсной последовательности для тактирования центрального процессора и межмодульных магистралей.

* Устройство управления режимами работы МК, такими, как активный режим, в котором МК выполняет прикладную программу, режимы пониженного энергопотребления, в один из которых МК переходит, если по условиям работы выполнение программы может быть приостановлено, состояния начального запуска (сброса) и прерывания.

Базовый функциональный блок принято называть процессорным ядром МК. Процессорное ядро обозначают именем семейства МК, основой которого оно является. Например, ядро НС05 — процессорное ядро семейства Motorola MC68HC05, ядро MCS-51 — ядро семейства МК Intel 8хС51, ядро РIС16 — процессорное ядро Microchip РIС16.

Изменяемый функциональный блок включает модули различных типов памяти, модули периферийных устройств, модули генераторов синхронизации и некоторые дополнительные модули специальных режимов работы МК. Каждый модуль имеет выводы для подключения его к внутренним магистралям МК. Это позволяет на уровне топологического проектирования "подсоединять" те или иные модули к магистралям процессорного ядра, создавая таким образом разнообразные по структуре МК в пределах одного семейства. Совокупность модулей, которые разработаны для определенного процессорного ядра, принято называть библиотекой периферийных модулей. Термин "библиотека периферийных модулей" недостаточно точно отражает современные тенденции структурной организации МК. Если ранее под произвольно объединяемыми в состав МК модулями подразумевались только модули периферийных устройств, то теперь выбирать предстоит в каждой из пяти функциональных групп:

* Модули памяти.

* Модули встроенных генераторов синхронизации.

* Модули периферийных устройств.

* Модули контроля за напряжением питания и ходом выполнения программы.

* Модули внутрисхемной отладки и программирования.

Термин "модуль памяти" в применении к МК стал использоваться на этапе перехода к новым технологиям создания резидентной памяти программ и данных. Энергонезависимая память типа FLASH и EEPROM имеет не только режимы хранения и чтения информации, которая была в нее записана до начала эксплуатации изделия на этапе программирования, но и режимы стирания и программирования под управлением прикладной программы. Вследствие этого энергонезависимая память типа FLASH и EEPROM требует управления режимами работы, для чего снабжена дополнительными блоками управления и регистрами специальных функций. Массив ячеек памяти, доступных для чтения, стирания и записи информации, дополнительные аналоговые и цифровые схемы управления, а также регистры специальных функций объединены в функциональный блок, который и носит название модуля памяти.

Существенное изменение претерпели также генераторы синхронизации МК. Во-первых, произошло функциональное разделение собственно генератора синхронизации, который выделился в отдельный модуль, и схемы формирования многофазной последовательности импульсов для тактирования центрального процессора и межмодульных магистралей, которая является неотъемлемой частью процессорного ядра. Во-вторых, появилась возможность выбора внешнего времязадающего элемента: кварцевый или керамический резонатор, RC-цепь. Схемотехника выполнения усилителей с положительной обратной связью определяется типом времязадающего элемента, соответственно появились разные модификации модулей встроенного генератора синхронизации. В-третьих, повышение производительности процессорного ядра МК связано с повышением частоты тактирования центрального процессора и межмодульных магистралей. Однако применение высокочастотных кварцевых резонаторов в качестве времязадающего элемента повышает уровень электромагнитного излучения, т.е. возрастает интенсивность генерации помех. Кроме того, высокочастотные кварцевые резонаторы являются относительно дорогим элементом. Поэтому современные генераторы синхронизации имеют в своем составе умножитель частоты с программно настраиваемым коэффициентом. Умножитель частоты часто выполняется по схеме синтезатора с контуром фазовой автоподстройки частоты(PLL — Phase Loop Lock). Цепи синтезатора частоты и регистры специальных функций для управления режимами его работы объединены в модуль синхронизации.

Группа модулей периферийных устройств включает большинство из известных типов адаптеров сопряжения с объектом:

* Параллельные порты ввода/вывода с возможностью индивидуальной настройки направления передачи каждой линии.

* Многорежимные таймеры/счетчики, таймеры периодических прерываний, процессоры событий.

* Контроллеры последовательного интерфейса связи нескольких типов (SCI, SPI, CAN).

* Многоканальный АЦП.

* Контроллеры ЖК-индикаторов и светодиодной матрицы. Относительно новыми для 8-разрядных МК являются две последние группы модулей. Первые осуществляют диагностику некоторых подсистем МК и позволяют восстановить работоспособность устройства на основе МК при нарушениях программного характера, сбоях в системе синхронизации, снижении напряжения питания. Вторые являются аппаратной основой режимоввнутрисхемной отладки и программирования в системе, которые позволяют отлаживать прикладную программу и заносить коды программы в энергонезависимую память МК прямо на плате конечного изделия, без использования дополнительных аппаратных средств отладки и программирования.

2. ПРОЦЕССОРНОЕ ЯДРО МК

Процессорное ядро представляет собой неразрывное единство трех составляющих его технического решения:

1. Архитектуры центрального процессора с присущими ей набором регистров для хранения промежуточных данных, организацией памяти испособами адресации операндов в пространстве памяти,системой команд, определяющей набор возможных действий над операндами, организациейпроцесса выборки и исполнения команд.

2. Схемотехники воплощения архитектуры, которая определяет последовательность перемещения данных по внутренним магистралям МК между регистрами, арифметическо-логическим устройством и ячейками памяти в процессе выполнения каждой команды.

3. Технологии производства полупроводниковой БИС МК, которая позволяет разместить схему той или иной сложности на полупроводниковом кристалле, определяет допустимую частоту переключении в схеме и энергию потребления.

Эти три составляющие неразрывно связаны друг с другом и в конечном счете определяют важнейший параметр процессорного ядра МК — его производительность.

Ядро современных 8-разрядных МК реализует один из двух принципов построения МП:

* МП с CISC-архитектурой — МП с полной системой команд (Complicated Instruction Set Computer).

* МП с RISC-архитектурой — МП с сокращенной системой команд (Reduced Instruction Set Computer).

В применении к 8-разрядным МК микропроцессор с CISC-архитектурой имеет однобайтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. Выборка команды из памяти осуществляется побайтно в течение нескольких циклов синхронизации МК. Время выполнения каждой команды с учетом времени выборки составляет от 1 до 10 циклов. Длительность цикла синхронизации равна периоду частоты тактирования внутренних магистралей fbus. К МК с CISC-архитектурой относятся семейства НС05 и НС08 фирмы Motorola, МК с ядром MCS-51, которое было предложено фирмой Intel, а в настоящее время поддерживается сразу несколькими производителями (Atmel, Philips, Dallas), МК семейства С500 фирмы Infineon и ряд других.

МП с RISC-архитектурой имеет формат команды фиксированной длины (например, 12 или 14 бит), выборка команды из памяти иееисполнение осуществляются за один цикл синхронизации МК. К МК с RISC-архитектурой относятся МК AVR фирмы Atmel, МК РIС16 и РIС17фирмы Microchip, МК фирмы Scenix.

По определению МК с RISC-архитектурой должны иметь более высокую производительность по сравнению с CISC МК при одной и той же частоте fbus, т.к. первые выполняют каждую команду за один такт, а последние — за несколько. Однако на практике вопрос о производительности является значительно более сложным и почти всегда неоднозначным:

* Указанная в справочных данных частота синхронизации обычно соответствует частоте подключаемого кварцевого резонатора fxclk, в то время как длительность цикла центрального процессора определяется частотой обмена по внутренним магистралям адреса и данных fbus. Соотношение fxclк и fbusиндивидуально для каждого ядра МК. Так, для ядра Intel MCS-51 f x clk/fbus =12, для ядра Motorola HC05 f x clk/fbus = 2, для Microchip Р1С16 f x clk/fbus = 4, для Scenix f x clk/fbus = 1. В МК Motorola НС08 тактирование осуществляется с использованием умножителя частоты и fbus > f x clk. Поэтому при оценке производительности следует сравнивать только максимальную частоту тактирования межмодульных магистралей fbus. Численные значения fbus для популярных семейств 8-разрядных МК приведены в табл.1.

Табл. 1. Частота тактирования межмодульных магистралей 8-разрядных МК

| Семейство МК | Архитектура ядра | fbus max [МГц] | fxclk/fbus | fxclk max [МГц] | |

| МК, ПРОГРАММНО СОВМЕСТИМЫЕ С ЯДРОМ MCS-51 | |||||

| Intel MCS-51 | CISC | ||||

| Atmel 89С55 | CISC | 2.75 | |||

| Infenion С500 | CISC | 3.3 | |||

| Philips 9С51/52 | CISC | 2.75 | |||

| Philips 8051XA | CISC | - | |||

| Dallas High Speed | CISC | 8.25 | |||

| МК С ДРУГИМИ ТИПАМИ ПРОЦЕССОРНОГО ЯДРА | |||||

| Motorola HC05 | CISC | ||||

| Motorola HC08 | CISC | 4 или <1 | |||

| Motorola HС11 | CISC | ||||

| MicrochipPIC16 | RISC | ||||

| MicrochipPIC17 | RISC | 8.25 | |||

| Microchip PIC18 | RISC | ||||

| Atmel AVR | RISC | ||||

| Scenix | RISC | ||||

* Производительность МП, и МК в том числе, принято оценивать числом операций пересылки "регистр-регистр", которые могут быть выполнены в течение одной секунды. Для МК с RISC-архитектурой время выполнения любой операции составляет 1/fbus, следовательно, их производительность равна fbus оп/с. Например, производительность PIC16 составляет 5 млн. оп/с, Scenix — 25 млн. оп/с. В МК с CISC-архитектурой число циклов выполнения операции "регистр-регистр" составляет от 1 до 3, что снижает производительность.

* Однако такая оценка производительности является общей. Она не учитывает особенности алгоритмов управления, используемых в каждой конкретной области применения. Так, при разработке быстродействующих регуляторов основное внимание следует уделять времени выполнения операций умножения и деления, которые требуются при реализации уравнений различных передаточных функций. А при реализации кнопочной станции кабины лифта следует оценивать время выполнения только логических функций, которые используются при опросе клавиатуры и при генерации протокола последовательного интерфейса связи с контроллером управления движения, который оптимизирует перемещение между этажами сразу нескольких кабин лифта. В задачах оптимального управления по таблицам, которые характерны для устройств силовой электроники, на первый план выходит возможность быстрого перебора больших таблиц данных. Поэтому в критических ситуациях, связанных с требованиями высокого быстродействия, следует оценивать производительность на основе тех операций, которые преимущественно используются в алгоритме управления и имеют ограничение по времени выполнения.

В задачах управления объектом в реальном времени существует еще один очень важный фактор производительности, который никак не отображается числом операций в секунду. Это время перехода на подпрограмму прерывания по запросу внешнего устройства или периферийного модуля. В процессе перехода на подпрограмму прерывания каждый МК должен распознать запрос на прерывание, дождаться завершения выполнения текущей команды, сохранить значение программного счетчика PC и некоторые регистры центрального процессора в стеке, загрузить вектор прерывания, выполнить некоторые вспомогательные команды и лишь затем приступить к выполнению алгоритма обслуживания устройства, которое вызвало это прерывание. Суммарное время перехода на подпрограмму прерывания определяется архитектурой процессорного ядра МК и частотой его тактирования.

3. РЕЗИДЕНТНАЯ ПАМЯТЬ МК

Закрытая архитектура современных 8-разрядных МК стала реализуемой лишь при условии интеграции на кристалл МК модулей памяти двух типов: энергонезависимого запоминающего устройства для хранения кодов прикладных программ (ПЗУ) и оперативного запоминающего устройства для хранения промежуточных результатов вычислений (ОЗУ). С момента появления МК технология энергонезависимых запоминающих устройств претерпела множество изменений, которые позволили не только повысить информационную емкость, быстродействие, надежность хранения информации, но и привели к появлению принципиально новых технологий программирования резидентной памяти МК. С точки зрения пользователей МК следует различать пять типов энергонезависимой резидентной памяти:

* ПЗУ масочного типа — mask-RОM. Содержимое ячеек ПЗУ этого типа записывается на заводе-изготовителе МК с помощью масок и не может быть заменено или "допрограммировано" в области ранее не использованного сегмента памяти, Поэтому МК с таким типом памяти программ следует использовать только после достаточно длительной опытной эксплуатации изделий. Первые образцы масочных ПЗУ появились в начале 60-х гг., но даже сегодня ПЗУ масочного типа — самое дешевое и эффективное решение при больших объемах выпускаемой аппаратуры. Использование МК с масочным ПЗУ экономически становится рентабельным при партии в несколько десятков тысяч штук. Кроме благоприятных экономических аспектов, решения с ПЗУ масочного типа имеют и другое преимущество. Они обеспечивают высокую надежность хранения информации по причине программирования в заводских условиях с последующим контролем качества. Недостатки ПЗУ масочного типа очевидны: любое изменение прикладной программы потребует новой серии ИС, что может оказаться весьма дорогостоящим и трудоемким решением.

* ПЗУ, однократно программируемые пользователем — OTPROM (One-Time Programmable ROM). В незапрограммированном состоянии каждая ячейка памяти модуля однократно программируемого ПЗУ при считывании возвращает код $FF. Программированию подлежат только те разряды, которые после программирования должны содержать 0. Если в процессе программирования некоторые разряды какой-либо ячейки памяти были установлены в 0, то восстановить в этих разрядах единичное значение уже невозможно. Поэтому рассматриваемый тип памяти и носит название "однократно программируемые ПЗУ". Однако те разряды, которые в процессе предшествующего сеанса программирования не изменялись, т.е. имеют единичные значения, могут быть подвергнуты программированию в последующем и "доустановлены" в 0. Число возможных сеансов программирования модуля однократно программируемого ПЗУ в составе МК не имеет ограничений. Технология программирования состоит в многократном приложении импульсов повышенного напряжения к элементарным ячейкам адресуемого байта памяти (битам), подлежащим программированию. Уровень напряжения программирования, число импульсов и их временные параметры должны в точности соответствовать техническим условиям. В противном случае ячейки памяти могут восстановить единичное значение по прошествии некоторого времени (иногда нескольких лет) или при изменении условий работы. МК с однократно программируемым ПЗУ рекомендуется использовать в изделиях, выпускаемых небольшими партиями.

* ПЗУ, программируемые пользователем, с ультрафиолетовым стиранием — EPROM (Erasable Programmable ROM). ПЗУ данного типа допускают многократное программирование. Технология программирования близка к технологии однократно программируемых ПЗУ. Перед каждым сеансом программирования для восстановления единичного значения ранее запрограммированных ячеек памяти весь модуль ПЗУ должен быть подвергнут операции стирания при помощи ультрафиолетового облучения. Для этого корпус МК выполнен со специальным стеклянным окном, внутри которого расположена пластина ИС МК. Но если некоторые разряды ячеек памяти должны быть "допрограммированы" с 1 на 0 при неизменном состоянии ранее запрограммированных разрядов, то операция стирания может быть пропущена. Число сеансов стирания/программирования ПЗУ данного типа ограничено и составляет 25...100 при условии соблюдения технологии программирования (напряжение, число и длительность импульсов программирования) и технологии стирания (волновой диапазон источника ультрафиолетового излучения). МК с ПЗУ данного типа имеют высокую стоимость, поэтому их рекомендуется использовать только в опытных образцах изделий.

* ПЗУ, программируемые пользователем, с электрическим стиранием - EEPROM, (Electrically Erasable Programmable ROM). Электрически программируемые и электрически стираемые ПЗУ совместили в себе три положительных качества рассмотренных выше типов памяти. Во-первых, ПЗУ типа EEPROM программируются пользователем; во-вторых, эти ПЗУ могут быть многократно подвергнуты операции стирания и, следовательно, многократно программируются пользователем; в-третьих, эти ПЗУ дешевле ПЗУ с ультрафиолетовым стиранием. Максимальное число циклов стирания/программирования ПЗУ типа EEPROM в составе МК обычно равно 10000. Для сравнения: тот же тип памяти в отдельном корпусе допускает 106 циклов стирания/программирования. Технология программирования памяти типа EEPROM позволяет реализоватьпобайтовое стирание и побайтовое программирование, для чего к выбранной ячейке памяти должно быть приложено относительно высокое напряжение 10...20 В. Однако допускается также одновременное стирание некоторого количества ячеек памяти с последовательными адресами, т.е. стирание блока памяти. Несмотря на очевидные преимущества, редкие модели современных МК используют ПЗУ типа EEPROM для хранения программ. Виной тому два обстоятельства. Во-первых, ПЗУ типа EEPROM имеют ограниченную емкость и могут использоваться в качестве резидентной памяти программ только в маловыводных МК с небольшим объемом памяти. Во-вторых, почти одновременно с EEPROM ПЗУ появились ПЗУ типа FLASH, которые обеспечивают близкие пользовательские характеристики, но значительно дешевле.

*ПЗУ с электрическим стиранием типа FLASH — FLASH ROM. Электрически программируемые и электрически стираемые ПЗУ типа FLASH были предназначены для заполнения "ниши" между дешевыми однократно программируемыми ПЗУ большой емкости и дорогими EEPROM ПЗУ малой емкости. ПЗУ типа FLASH сохранили преимущества, присущие EEPROM: возможность многократного стирания и программирования посредством приложения повышенного напряжения. Однако для увеличения объема памяти транзистор адресации каждой элементарной ячейки был удален, что не дает возможности программировать каждый бит памяти отдельно.Память типа FLASH стирается и программируется страницами или блоками. Страница, как правило, составляет 8, 16 или 32 байта памяти, блоки могут объединять некоторое число страниц, вплоть до полного объема резидентного ПЗУ МК (до 60 КБайт). Упрощение декодирующих схем, произошедшее из-за уменьшения числа транзисторов и, как следствие, снижение стоимости и размеров привело к тому, что МК с FLASH-памятью программ в настоящее время становятся конкурентоспособными по отношению не только к МК с однократно программируемым ПЗУ, но и с масочным ПЗУ также.

Первый тип памяти (mask-ROM) предполагает программирование МК только в заводских условиях. Второй и третий тип памяти (ОTPROM и EPROM) в режиме программирования требуют подключения источника повышенного напряжения к одному из выводов МК. Для их программирования используются специальные программаторы, в которых требуемая последовательность импульсов программирования с амплитудой 10...25 В создается внешними по отношению к МК средствами. Технология программирования памяти первых трех типов не предполагает изменения содержимого некоторых ячеек энергонезависимой памяти в процессе работы устройства под управлением прикладной программы.

Память типа EEPROM и FLASH также требует в процессе стирания/программирования приложения повышенного напряжения. В ранних образцах МК (например, Microchip PIC16C5xx) это напряжение должно было быть подано на один из выводов МК в режиме программирования. В новейших версиях МК (Motorola HC08 и Microchip РIС16) модули FLASH и EEPROM ПЗУ содержат встроенные схемы повышающих преобразователей напряжения, которые называют генераторами накачки. Допускается включение и отключение генератора накачки под управлением программы посредством установки битов в регистрах специальных функций модулей памяти. Следовательно, появилась принципиальная возможность осуществить программирование или стирание ячеек памяти FLASH и EEPROM ПЗУ в процессе управления объектом, без останова выполнения прикладной программы и перевода МК в режим программирования. Вспомним разницу между EEPROM и FLASH ПЗУ в составе МК: EEPROM ПЗУ практически никогда не используется для хранения программ, но оно имеет режим побайтового программирования. Предоставленная техническая возможность программирования под управлением прикладной программы становится реализуемой, т.к. носителем программы в МК является другой модуль памяти. Следовательно, в процессе программирования повышенное напряжение не прикладывается к носителю программы алгоритма программирования и эта программа может быть выполнена в обычном режиме. Данное обстоятельство сделало EEPROM память идеальным энергонезависимым запоминающим устройством для хранения изменяемых в процессе эксплуатации изделия настроек пользователя. В качестве примера достаточно вспомнить современный телевизор или музыкальный центр: настройки каналов сохраняются при отключении питания. Одной из тенденций совершенствования резидентной памяти 8-разрядных МК стала интеграция на кристалл МК сразу двух модулей энергонезависимой памяти: ОТР или FLASH для хранения программ и EEPROM для хранения перепрограммируемых констант.

Дата добавления: 2015-07-25; просмотров: 65 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Нормативные правовые акты | | | Аннотация 2 страница |