Читайте также:

|

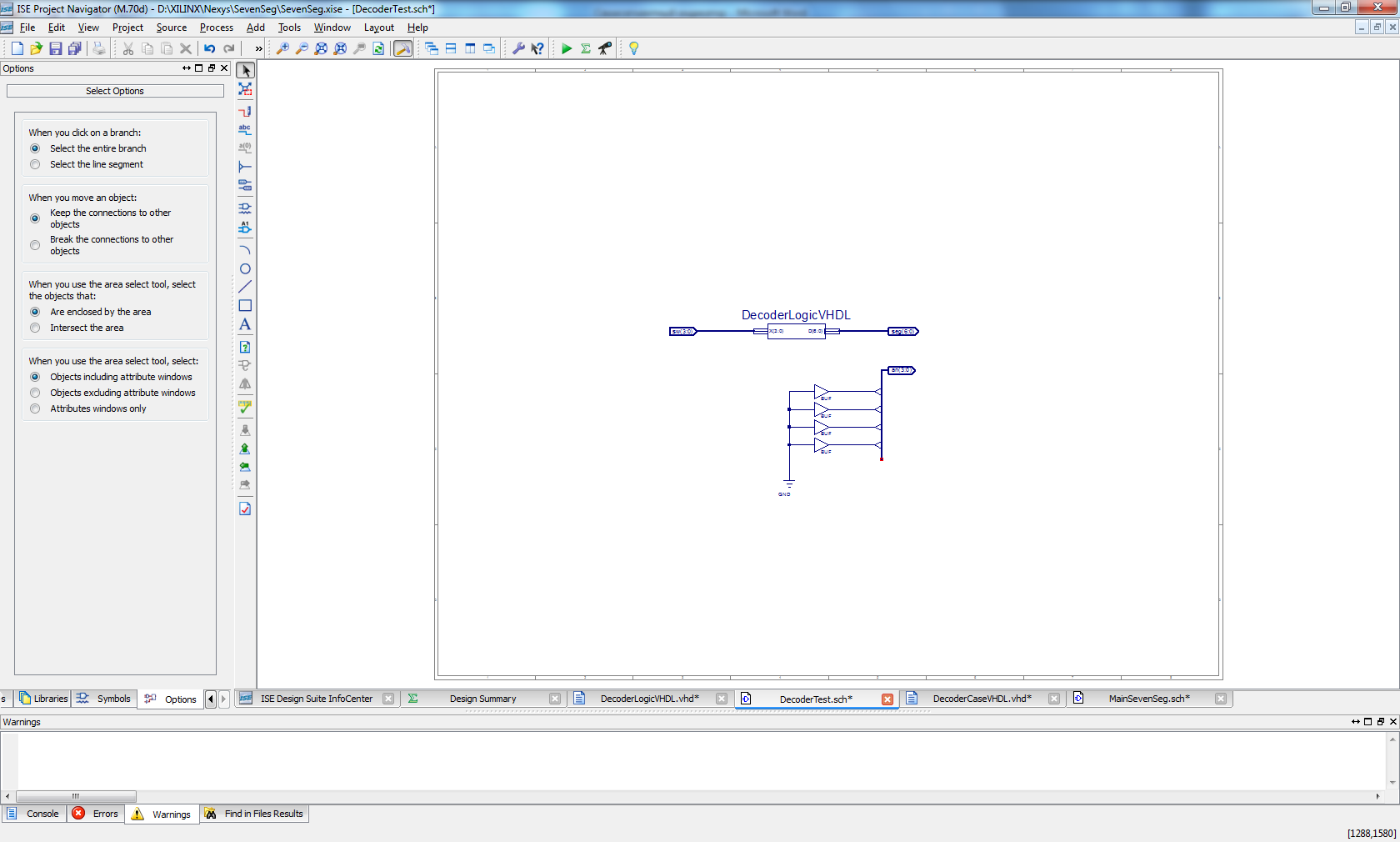

Для демонстрации работы разработанных дешифраторов, преобразуем схему MainSevenSeg согласно рис.13.

Рис. 13. Тестовая схема прошивки

Описание связей выходов схемы с выходами на отладочной плате описывается в *.ucf файле, создание которого показано на рис. 14.

Рис. 14. Создание ucf файла

Далее прописываются связи, для схемы Basys 2:

NET "sw<0>" LOC = "P11";

NET "sw<1>" LOC = "L3";

NET "sw<2>" LOC = "K3";

NET "sw<3>" LOC = "B4";

NET "an<0>" LOC = "K14";

NET "an<1>" LOC = "M13";

NET "an<2>" LOC = "J12";

NET "an<3>" LOC = "F12";

NET "seg<0>" LOC = "L14"; #a

NET "seg<1>" LOC = "H12"; #b

NET "seg<2>" LOC = "N14"; #c

NET "seg<3>" LOC = "N11"; #d

NET "seg<4>" LOC = "P12"; #e

NET "seg<5>" LOC = "L13"; #f

NET "seg<6>" LOC = "M12"; #g

Следующим шагом является создание файла прошивки. Для этого выбирается основной файл проекта (рис. 15.а) и строка Rerun All контекстное меню для Generate Programming File (рис. 15.б).

а) б)

Рис. 15. Создание файла прошивки

Файл прошивки имеет разрешение bit, для данного проекта его название mainsevenseg.bit. Следующим шагом является прошивка ПЛИС, выполняемая при помощи программы Digilent Adept.

Дата добавления: 2015-07-20; просмотров: 48 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Реализация на языке VHDL | | | Мультиплексирование семисегментных индикаторов |