Читайте также:

|

Модуль последовательного периферийного интерфейса 8P108 предназначен для вы- сокоскоростного обмена между МК и периферийными микросхемами, такими как АЦП и ЦАП, FLASH-пaмять большой информационной емкости, часы реального времени. Модуль SP108 обладает следующими характеристиками:

· поддерживает два режима работы: ведущего (master) и ведомого (slave) приемо передатчиков;

· позволяет программно настраивать частоту обмена, причем в формировании сетки частот модули таймеров Т1М08 и Р1Т08 не задействованы:

где  = 2, 8, 32, 128; максимальная частота обмена в режиме ведущего составляет 4,0 МГц, в режиме ведомого – 8,0 МГц;

= 2, 8, 32, 128; максимальная частота обмена в режиме ведущего составляет 4,0 МГц, в режиме ведомого – 8,0 МГц;

· генерирует запросы на прерывание c раздельными векторами по завершению приема

очередного байта или по окончании передачи байта;

· генерирует два флага нарушения режима работы: при переполнении приемника и

при принудительной смене режима работы (ведущей/ведомый) в процессе незавершенного обмена;

· позволяет программно конфигурировать линии приема и передачи данных (Mi50 и MOS1) как линии с открытым коллекторным выходом; объединение М1S0 и M031 по схеме «монтажное ИЛИ» делает модуль совместимым с протоколом интерфейса 120.

Контроллер 5Р108 обслуживает стандартную шину S[01, для чего имеет четыре линии:

MOS1 – линия передачи данных от ведущего к ведомому (Master Output Slave Input); Mi80 –линия передачи данных от ведомого к ведущему (Master Input Slave Output); SPSCK – линия сигнала синхронизации данных;

SS – линия выбора ведомого.

Направление передачи каждой линии определяется выбором режима работы контроллера SP108. Если назначен режим ведущего (бит MSTR регистра управления SPCR равен 1), то линии МОS1 и SCK работают в режиме вывода, а линия MISO в режиме ввода. Если назначен режим ведомого (MSTR = 0), то линии M0S1, SCK и SS работают в режиме ввода, а MIS0 – в режиме вывода. В режиме ведущего линия SS может быть использована, как обычная линия ввода/вывода.

Обслуживание модуля SP108 является альтернативной функцией для линий РТО. Если бит разрешения работы контроллера модуля установлен SРЕ = 1, то независимо от значения соответствующих битоd регистра направления передачи порта ввода/вывода его линии назначаются для работы в составе контроллера SP108.

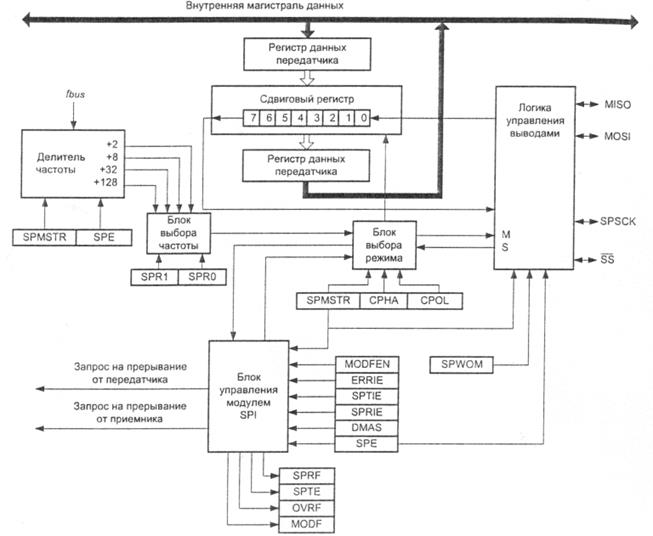

Функциональная схема контроллера 51'108 приведена на рис. 4.1. Основные элементы контроллера – 8-разрядный сдвиговый регистр (Shift Register) и два буферных регистра данных, программно доступных по одному и тому же адресу. При выполнении операции записи в регистр данных SPDR данные будут запомнены в буферном регистре передатчика. Буфер данных передатчика недоступен для чтения. Операция чтения регистра SPDR возвращает данные из буферного регистра приемника. Буфер данных приемника недоступен для записи.

Если контроллер настроен для работы в режиме ведущего, то обмен данными в любом из направлений (прием или передача) инициируется операцией записи байта в регистр данных. Этот байт сначала автоматически копируется в сдвиговый регистр, а затем сдвигается в течение 8 тактов генератора синхронизации обмена на линию M0SI. Одновременно на линию SCK выдаются импульсы синхронизации. Каждый из импульсов синхронизации SCK, поступающих от ведущего на одноименный вход ведомого, вызывает операцию сдвига данных на один разряд в сдвиговом регистре принимающего устройства. В результате очередной бит, переданный ведущим по линии MOSI, запоминается в регистре-приемнике, но одновременно на линию M1S0 выдвигается очередной старший бит этого регистра. Бит с линии MIS0 фиксируется в сдвиговом регистре ведущего. При завершении передачи 8 бит данных от ведущего к ведомому в сдвиговом регистре ведущего окажется принятый байт данных от ведомого. Если пользователь желает реализовать передачу байта данных от ведущего к ведомому, то для осуществления обмена в программе ведущего в регистр данных контроллера SP108 записывается передаваемый байт, а при завершении передачи бесполезные данные из регистра данных порта SP108 просто не считываются. Если же пользователь желает реализовать прием байта данных, то для осуществления обмена в программе ведущего в регистр данных контроллера SP108 записывается любой «ненужный» байт, а при завершении передачи принятый полезный байт данных считывается из регистра данных порта SР108. Завершение передачи каждого байта данных отмечается установкой в «1» бита SPIF регистра состояния SPSR. Этот бит генерирует запрос на прерывание, если прерывания от модуля SPI разрешены (бит SPIЕ = 1). При обмене с высокими скоростями в режиме ведущего бит завершения передачи байта SPIF следует контролировать программно. Для этого после записи очередного байта в регистр данных следует прочитать регистр состояния SPSR, дождаться, пока бит ВР1Р не установится, а затем произвести считывание принятых данных или запись следующего передаваемого байта в регистр данных (в зависимости от направления передачи).

Рис. 4.1. Функциональная схема контроллера SР108

Бит SPIF сбрасывается в «0» автоматически при выполнении последовательности из двух операций:

· чтение регистра состояния SPSR при установленном бите SPIF;

· чтение или запись в регистр данных SCDR.

Если контроллер SP108 работает в режиме ведомого, то момент начала передачи определяет ведущий. Поэтому следует организовать прерывания по запросу от триггера SPIF, в подпрограмме обработки которого принятый байт будет прочитан из регистра данных и проанализирован, а при необходимости предоставления ведущему каких-либо данных очередной байт будет записан в регистр данных для последующей передачи при поступлении импульсов синхронизации SCK от ведущего.

Контроллер SP108 поддерживает 4 возможных режима SPI. Для задания детализированной временной диаграммы обмена следует использовать биты СРНА и CPOL регистра управления SPCR. Скорость обмена в режиме ведущего определяется программно настраиваемым коэффициентом делителя  (биты SPR1:SPRO регистра управления). Максимальная скорость обмена составляет

(биты SPR1:SPRO регистра управления). Максимальная скорость обмена составляет  /2, минимальная -

/2, минимальная -  /128. В режиме ведомого биты SPR1:SPR0 не оказывают влияния на работу контроллера. Скорость обмена определяется ведущим, она может достигать

/128. В режиме ведомого биты SPR1:SPR0 не оказывают влияния на работу контроллера. Скорость обмена определяется ведущим, она может достигать

Программно-логическая модель модуля 81'108 включает три регистра специальных функций:

1) SPCR - регистр управления модуля SP108;

2) SPSCR - регистр состояния модуля SP108;

3) SPDR - регистр данных модуля SP108.

Форматы регистров SPCR и SPSCR приведены в табл. 4.1 и 4.2. Регистр данных SPDR доступен по адресу 0012h.

Таблица 4.1

Формат регистра SPCR

| SPCR | Регистр управления модуля SP108 | |||||||

| 7 6 5 4 3 2 1 0 | ||||||||

| SPRIE | х | SPMSТR | СРОL | CРНА | SPWOM | SPE | SРТlЕ | |

| Состояние при сбросе: 28h Адрес OO10h | ||||||||

| Имя бита | Назначение бита | |||||||

| SPRIE | Бит разрешения прерывания по запросу приемника модуля SP1 Бит разрешает генерацию запроса на прерывание при установленном бите SPRF: 1 — прерывания по запросу приемника разрешены; 0 — прерывания по запросу приемника запрещены. Биты доступен для чтения и для записи. При сбросе прерывания от приемника запрещаются. | |||||||

| SPMSTR | Бит режима работы контроллера SPI 1 — контpoллер SPI работает в режиме ведущего (Master); 0 —контроллер SPI работает в режиме ведомого (slave). Бит доступен для чтения и для записи. При сбросе назначается режим ведомого. | |||||||

| CPOL | Бит выбора полярности сигнала синхронизации SCK Этот бит определяет состояние линии SCK (вывод SPSCK) между сеансами передачи данных. Бит CPOL вместе с битом СРНА задает один из четырех возможных режимов SP1 интерфейса: 1 - SCK = 1 - между сеансами передачи данных; 0 - SCK = 0 - между сеансами передачи данных. Бит доступен для чтения и для записи. После сброса МК CPOL = 0. | |||||||

| СРНА | Бит выбора фазы сигнала синхронизации SCK Этот бит определяет протокол обмена по 5Р1-шине. Если СРНА = 0, то начало обмена инициируется установкой сигнала выбора ведомого SS а активное состояние (режимы 0 и 1). Первый перепад сигнала синхронизации SCK используется принимающим устройством для запоминания очередного бита в сдвиговом регистре. Передающее устройство выставляет очередной бит посылки на линии MOSI по каждому четному фронту сигнала SCK. Сиг‑ нал на линии выбора ведущего SS должен быть возвращен в неактивное состояние после передачи каждого байта в любом направлении (рис. 4.25). Если СРНА = 1, то начало обмена определяет первое изменение уровня сигнала на линии SCK после установки сигнала выбора ведомого SS в активное состояние (режимы 2 и 3). Все нечетные перепады SCK вызывают выдвижение очередного бита посылки из сдвигового регистра передатчика на линию. Каждый четный перепад используется для записи этого бита в сдвиговый регистр приемника. Сигнал выбора ведомого может оставаться в активном состоянии SS = 0 в течение передачи нескольких байт информации (рис. 4.26). Бит доступен для чтения и для записи. После сброса МК СРНА = 1. | |||||||

| SPWOM | Бит выбора режима открытого коллектора

Этот бит определяет состояние выходных буферов линий M0SI, МIS0,

SPSCK:

1 - буферы переведены в режим открытого коллекторного выхода;

0 - буферы работают в режиме двунаправленной передачи с возможностью

установки в высокоимпедансное состояние.

Перевод линий М0S1 и МIS0 в режим открытого коллектора позволяет

соединить их по схеме «монтажное ИЛИ», что делает интерфейс SPI совместимым с интерфейсом I  С. Бит доступен для чтения и для записи. После

сброса SPWOM = 0. С. Бит доступен для чтения и для записи. После

сброса SPWOM = 0.

| |||||||

| SPE | Бит разрешения работы модуля SPI 1 - контроллер SРI включен; 0 –контроллер SPI выключен. Бит доступен для чтения и для записи. При сбросе МК контроллер SPI отключается. |

| SPTIE | Бит разрешения прерывания по запросу передатчика модуля SPI Бит разрешает генерацию запроса на прерывание при установленном бите SPTE: 1 -прерывания по запросу передатчика разрешены; 0 - прерывания по запросу передатчика запрещены. Биты доступен для чтения и для записи. При сбросе прерывания от пере‑ датчика запрещаются. |

Тaблица 4.41

Формат регистра SPSCR

| SPSCR | Регистр управления модуля SP108 | |||||||

| 7 6 5 4 3 2 1 0 | ||||||||

| SPRF | ERRIE | OVRF | MODF | SРТЕ | MODFEN | SPR1 | SPR0 | |

| Состояние при сбросе: 08h Адрес 0011h | ||||||||

| Имя бита | Назначение бита | |||||||

| SPRF | Бит завершения приема байта данных Устанавливается в момент, когда принятые данные автоматически переписываются в буферный регистр данных приемника. Бит SPRF генерирует запрос на прерывание, если бит SPRIE установлен. Сбрасывается в «0» автоматически при выполнении последовательности из двух операций: • чтение регистра состояния SPSCR при установленном бите SPRF; • чтение из регистра данных SPDR принятого байта данных. Бит доступен только для чтения. При сбросе МК бит устанавливается в «0». | |||||||

| ERRIE | Бит разрешения прерывания по флагам ошибки OVRF и МОDF Этот бит разрешает генерацию запроса на прерывание при установке в «1» флага нарушения режима MODF и флага ошибки приема OVRF: 1 — прерывания по флагам OVRF и МОDF разрешены; 0 — прерывания по флагам OVRF и MODF IDLE запрещены. Бит доступен для чтения и для записи. При сбросе прерывания по флагам ошибки запрещаются. | |||||||

| OVRF | Бит ошибки приема Устанавливается при попытке записи аппаратными средствами приемника очередного принятого байта из сдвигового регистра в буферный регистр данных в то время, как предыдущие данные из буферного регистра еще не считаны (бит SPRF установлен). При таком стечении обстоятельств содер‑ жимое буферного регистра приемника сохраняется, а второй принятый байт теряется. Бит OVRF сбрасывается в «0» автоматически при выполнении последовательности из двух операций: • чтение регистра состояния SPSCR при установленном бите OVRF; • чтение из регистра данных SPDR первого принятого байта данных. Бит доступен только для чтения. При сбросе МК бит устанавливается в «0». | |||||||

| MODF | Бит нарушения режима контроллера SPI Устанавливается, если на линию SS ведущего подали сигнал низкого логи‑ ческого уровня или если на линию SS ведомого подали сигнал высокого ло‑ гического уровняв процессе незавершенного обмена. Сбрасывается в «0» автоматически при выполнении последовательности из двух операций: • чтение регистра состояния SPSCR при установленном бите МООР; • запись в регистр данных 3PDR.6ит доступен толь ко для чтения. При сбросе МК бит устанавливается в «0». | |||||||

| SPTE | Бит готовности буфера передатчика к приему новых данных Устанавливается в момент, когда предварительно загруженные в регистр буфера передатчика данные автоматически переписываются в сдвиговый регистр передатчика. Однако процесс передачи нового байта из cдвигового регистра начнется только после того, как бит SPTE будет сброшен. Бит SPTE информирует МК о том, что буфер передатчика пуст, и в него может быть записан новый байт. Бит SPTE генерирует запрос на прерывание, если бит SРТIЕ установлен. Бит SPTE сбрасывается в «0» автоматически при вы‑ полнении операции записи в регистр данных SPDR Бит доступен только для чтения. При сбросе МК бит устанавливается в «1». |

| MODFEN | Бит разрешения работы логики нарушения режима МОDF 1 — работа и установка бита MODF разрешены; 0 —работа и установка бита MODF запрещены. Если бит MODFEN сброшен и контроллер SPI работает в режиме ведущего, то линия SS может быть использована как обычная линия ввода/выdода. Бит доступен для чтения и для записи. При сбросе МК устанавливается в «0». |

| ELSiB —ELSiA | Биты выбора скорости передачи

Биты SPR1— SPR0 определяют скорость обмена при работе контроллера в

режиме ведущего. В режиме ведомого скорость ограничена величиной fвus

SPR1 SPR0 Частота следования Значение частоты

Импульсов SKC следования при  0 0

0 0  4 МГц

0 1 4 МГц

0 1  2 МГц

1 0 2 МГц

1 0  250 кГц

1 1 250 кГц

1 1  62,5 кГц

После сброса МК значения битов равны 0, т, е. выбрана максимальная

скорость обмена. 62,5 кГц

После сброса МК значения битов равны 0, т, е. выбрана максимальная

скорость обмена.

|

Дата добавления: 2015-07-25; просмотров: 71 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Формат регистра РТхPUE | | | Часть первая. Ввод в «тему» наших отношений. |