|

Читайте также: |

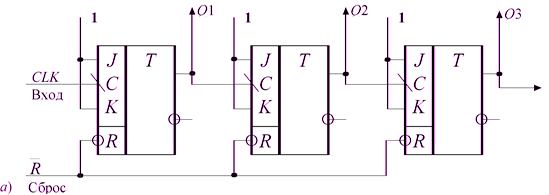

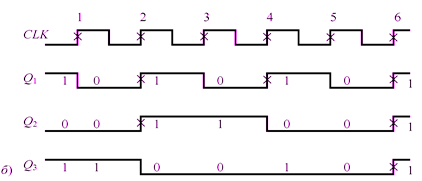

Рис. 3.1 Асинхронный суммирующий счетчик на JK- триггерах (а) и временная диаграмма его работы (б).

Асинхронные счетчики строятся в виде цепочки триггеров со счетным входом (JK - триггер с J=K =1 или D - триггер с инверсной обратной связью,  ), когда тактовый вход каждого последующего подключен к выходу Q или

), когда тактовый вход каждого последующего подключен к выходу Q или  предыдущего, что зависит как от направления счета, так и от типа тактирующего входа триггера.

предыдущего, что зависит как от направления счета, так и от типа тактирующего входа триггера.

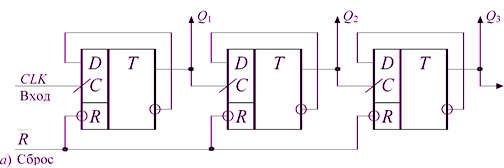

Схема суммирующего счетчика на JK - триггерах и временная диаграмма его работы приведены на рис. 3.1. Если тактовые входы JK - триггеров соединить с инверсными выходами предыдущих триггеров, то получится схема вычитающего счетчика. Аналогично, если в схеме вычитающего счетчика на D - триггерах (рис. 3.2.) тактовые входы триггеров соединить с инверсными выходами предыдущих триггеров, то счетчик станет суммирующим.

Полученные счетчики называют последовательными, так как в них каждый триггер переключается выходным сигналом предыдущего. Эти счетчики отличаются простой схемой, но низким быстродействием в режиме регистрации входных сигналов, так как в этом режиме нельзя подавать очередной входной сигнал, пока не зафиксировано предыдущее состояние счетчика. Время установления кода равно t уст = nt зд. тр, где t зд. тр - время задержки переключения триггера. Очевидно, что максимальная частота входных сигналов в режиме регистрации составляет f макс.рег=1/ t уст. Впрочем, в режиме деления входных импульсов максимальная частота их поступления будет ограничиваться быстродействием младшего триггера и составит f макс.дел=1/ t зд.тр.

Рис. 3. 2 Асинхронный вычитающий счетчик на D- триггерах (а) и временная диаграмма его работы (б).

Второй недостаток состоит в том, что из-за накопления временных сдвигов в разрядах в процессе установления кода, в счетчике возникают на короткие промежутки времени ложные состояния. Поэтому если к выходным разрядам такого счетчика подключить дешифратор, то на его выходах могут появиться ложные сигналы, соответствующие промежуточным фазам перехода счетчика из одного состояния в другое.

От названных недостатков свободны синхронные счетчики.

3.4. Синхронные двоичные счетчики

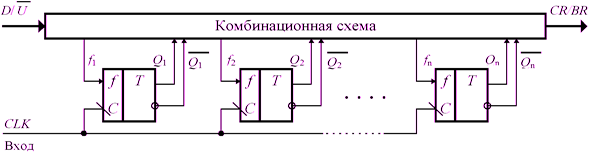

Рис. 3.3 Структурная схема синхронного счетчика

Схему синхронного счетчика можно представить обобщенной структурной схемой (рис. 3.3), включающей триггеры со счетным входом T и комбинационную схему, формирующую функции возбуждения fi для этих счетных входов. В JK - триггерах счетный вход организуется путем соединения входов J и K. Вход  управляет режимом работы схемы (

управляет режимом работы схемы ( - прямой счет,

- прямой счет,  - обратный счет), а выходной сигнал переноса/займа CR/BR (Carry/Borrow) может использоваться для наращивания разрядности счетчика.

- обратный счет), а выходной сигнал переноса/займа CR/BR (Carry/Borrow) может использоваться для наращивания разрядности счетчика.

Как следует из анализа табл. 3.1 (правило 2), переключение триггера младшего разряда осуществляется с приходом каждого счетного сигнала CLK, а остальных триггеров - только в том случае, когда все триггеры младших разрядов установлены в «1» (прямой счет) или в «0» (обратный счет).

Следовательно, в общем случае, функция возбуждения триггера fi для синхронного двоичного счетчика может быть определена выражением:

,

,  . (1)

. (1)

Для младшего разряда: f 1=1.

Сигнал переноса/заёма может формироваться в двух случаях, а именно, когда в счетчике хранится максимальное значение кода  при

при  и минимальное значение

и минимальное значение  при

при  :

:

. (2)

. (2)

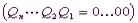

Рис. 3.5 Временная диаграмма формирования переноса и займа в 4-разрядном синхронном счетчике (CE =1)

На рис. 3.4 представлена схема 4-разрядного синхронного двоичного счетчика с изменяемым направлением счета, построенного в соответствии с выражениями (1) и (2) с тем отличием, что в схему введен дополнительный управляющий вход CE (Count Enable - разрешение счета). Временные диаграммы работы счетчика (рис. 3.5) поясняют особенности формирования переноса в режиме прямого счета и заёма - в обратном с учетом запаздывания в их формировании относительно счетного (тактового) сигнала CLK.

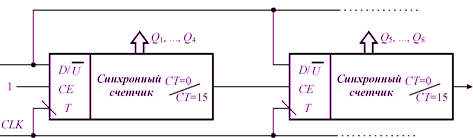

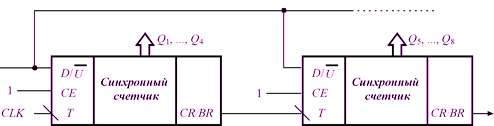

Каскадировать счетные группы можно двумя способами: с использованием последовательного или параллельного переносов. При параллельном переносе (рис. 3.6) две счетные группы как бы объединяются в единую синхронную схему 8- разрядного счетчика. Наличие управляющего входа разрешения счета CE при таком способе объединения является просто обязательным. Иногда, когда высокая скорость не требуется, счетные группы можно соединить последовательно (рис. 3.7), при этом сигнал переноса (заёма) служит тактовым сигналом следующей старшей группы. В этом случае (см. диаграммы рис. 3.5) вместо выхода  целесообразно использовать тот же сигнал, только синхронизированный тактовым сигналом (CR/BR). Схему же счетчика при этом можно упростить, убрав вход разрешения счета CE.

целесообразно использовать тот же сигнал, только синхронизированный тактовым сигналом (CR/BR). Схему же счетчика при этом можно упростить, убрав вход разрешения счета CE.

Рис. 3.6 Каскадирование синхронных счетчиков с параллельным переносом

Рис. 3.7 Каскадирование синхронных счетчиков с помощью последовательного переноса

Дата добавления: 2015-09-04; просмотров: 171 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Счётчики. Двоичные и двоично-десятичные счётчики. Построение. Индикация. Временные диаграммы. | | | Дизайн интерьера - стили и направления |