|

Читайте также: |

Регистры последовательных приближений предназначены для построения аналого-цифровых преобразователей (АЦП), в основу работы которых положен метод поразрядного уравновешения.

Суть метода: пусть нужно уравновесить напряжение 15 В. Расположим источники образцовых напряжений, значения кот подобраны в соответствии с двоичной системой счисления (16 В, 8 В, 4 В, 2 В, 1 В). Пусть эти напряжения включатся ключами, и остнуться вкл./выкл. В зависимости от того, какой знак разности между измеряемым напряжением и образцовым. Так, при приходе 1-го импульса включается напряжение 16 В. Разность 15-16=-1 имеет знак «-», поэтому это напряжение вкл-ся и в код числа, хар-щего состояние разрядов, записывается логич. ноль. Замем…8 В. Разность 15-8=7 В. Следовательно, это напряжение остается, и в код числа записывается логич единица. Потом подключают напряжение 4 В, кот суммируется с оставленным напряжением 8 В. Разность 15-8-4=3 В. Значит записывается единица. Дальше 2 В. Разность 15-8-4-2=1 В,опять логич единица. При подключении напряжения 1 В разность между уравновешивающим и измеряемым напряжениями равна 0 и в младшем разряде записывается лигич 1. Код числа, хар-щего образцовые напряжения, 0111. Т. о. в результате процесса уравновешивания получен код числа, кот-е однозначно хар-ет величину неизвестного сигнала.

Регистр послед. приближений- уст-во, с помощью кот обеспечивается управление ключами, включающими или отключающими образцовые напряжения или токи, и осуществляется формирование кода числа, хар-щего уравновешивающее напряжение или ток.

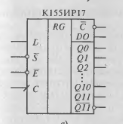

Работа регистра последовательных приближений: на вход D поступает информация с устройства сравнения. Запись информации производится за два такта на каждый разряд регистра. Вход С - вход этих самых тактов. Например, на вход D подается уровень лог. 1 и при воздействии тактового импульса в разряд, скажем, Q11 записывается эта единичка. Во втором такте этот бит либо подтверждается, либо отменяется, в зависимости от состояния входа D (его потенциала). После этого в третий такт уровень лог. 1, если он, конечно, есть на входе D, записывается в следующий разряд - Q10, а во втором такте также либо подтверждается, либо отменяется и так далее. После 24 тактов на выходе регистра, а именно на выходах Q0-Q11, записанное число оказывается цифровым эквивалентом аналоговой величины, воздействующей на входе устройства сравнения. Вход Е служит для разрешения работы регистра, вход S - вход стартового запуска (обычно эти сигналы инверсные), выход D0 - выход последовательного кода, С0 - выход конца преобразования.

Вопрос 72. Дешифраторы, принцип работы и назначение.

Дешифратор (декодер)– это устройство, преобразующее цифровой сигнал в какой-либо кодировке в другую, не закодированную форму. В условном обозначении дешифраторов (рис.1) на принципиальных схемах в основном поле прямоугольника пишут буквы DC.

(рис.1.)

(рис.1.)

В условных обозначениях микросхем о принадлежности к дешифраторам говорят буквы ИД.

Микросхемы дешифр-в часто имеют n входов и m выходов, m=2^n.

Входы дешифратора часто называют адресными, т.к. их сигналы характеризуют номер провода (адрес), на котором появится отличный от начального значения электрич.сигнал. Их часто нумеруют в соответствии с весами двоичных разрядов 2,4,6,8, 16… Число входов и выходов часто указывают так: дешифратор 3-8 (три в восемь).

Дешифраторы,кроме адресных, часто имеют разрешающий (управляющий, стобирующий) вход Е. При Е=1 дешифр.работает как обычно. При Е=0 на всех выходах устанавливаются уровни (нулевые и единичные),которые не зависят от кода, поданного на адресные входы. Вход Е мб инверсным. Подобные дешифраторы называют декодерами-демультипликсорами, что в условных обозначениях (вместо DC) DX.

В микросхемах дешифраторов обычно делают несколько разрешающих ходов. Они являются входами логического элемента И, установленного на входе. В этих случаях разрешающей комбинацией будет конъюнкция сигналов на входах Е, что показывается знаком &, записываем над буквой Е. Схемотехническая реализация дешифраторов может быть различной. Известны пирамидные, линейные и прямоугольные структуры. Кроме того,иногда различают одно-и многоступенчатые дешифраторы.

Пирамидные дешифраторы применяются крайне редко в связи с громоздкой структурой и наибольшей задержкой распространения сигнала. В них обычно исп-ся двухвходовые логические элементы.

Линейные относятся к числу наиболее быстродействующих, т.к. в них исп-ся всего одна ступень логич-х элем-в,с помощью которых проводится дешифрование входных данных.

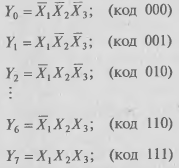

При построении дешифратора необходимо предварительно записать список ф-й,хар-х состояние каждого из его выходов. Так,если имеется 3 адресных входа Х1,Х2,Х3 и восемь выходов (m=2^n;2^3=8),то соответствующие ф-и могут иметь вид:

,где Х1 – вход первого (младшего) разряда цифрового слова, Х2 – вход второго разряда цифр.слова,Х3 – вход старшего разряда цифр.слова.

,где Х1 – вход первого (младшего) разряда цифрового слова, Х2 – вход второго разряда цифр.слова,Х3 – вход старшего разряда цифр.слова.

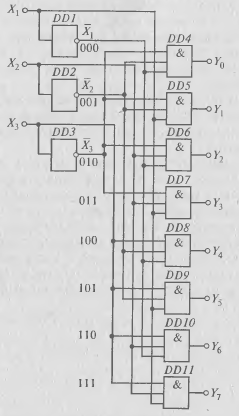

(рис.2. Схема дешифратора «три в восемь»)

(рис.2. Схема дешифратора «три в восемь»)

Инверторы DD1-DD3 введены для получения сигналов, инверсных входным (X1,X2,X3 (пишем со значком «вектора»)). Логические элементы И DD4-DD11 выполняют ф-ю дешифрования. Для этого на их входы подаются сигналы в соответствии с ф-й, характеризующей состояние данного выхода.

При четырёх и более адресных входах предпочитают применять двух- и многоступенчатые дешифраторы ввиду некоторой экономической выгоды таких технических решений.

Прямоугольный дешифратор относится к числу многоступенчатых. Он считается самым экономичным по аппаратурным затратам при большом количестве выходов(сотни и более). Это объясняется тем,что возможности простого линейн.дешифр.ограничены из-за небольшого числа входов у логич-х элем-в. При выполнении дешифр-а на основе готовых микросхем каскадное включение корпусов явл-ся более приемлимым.

Дата добавления: 2015-09-02; просмотров: 166 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Вопрос 70. Регистры хранения и сдвига, принцип работы регистров. | | | Вопрос 73. Шифраторы, назначение принцип действия. |