|

Читайте также: |

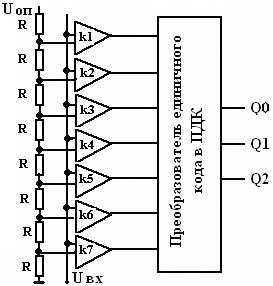

АЦП, выполненные по методу считывания или параллельные АЦП, совершают полное преобразование за один такт. Для этого в АЦП применяется 2n- 1 ‘эталон. В качестве примера представлена структурная схема трехразрядного параллельного АЦП напряжения в двоичный код (Рис.28.).

В этом АЦП входное напряжение Uвх сравнивается с семью эталонами, полученными делением стабильного опорного напряжения Uоп делителем напряжения. Для сравнения применяется 7 компараторов. Полученный параллельный единичный код преобразуется преобразователем в двоичный код.

Рис.28

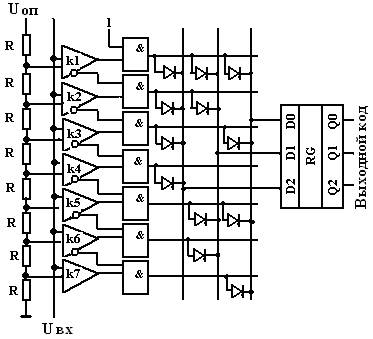

Время преобразования определяется временем задержки компараторов и преобразователя кода. К сожалению, преобразователи кода, выполненные на логических элементах, имеют большие времена задержки. В последнее время преобразование кода в параллельных АЦП делают на матричных диодных ПЗУ. Структура такого АЦП приведена на Рис.29.

Рис.29

В этой схеме применены компараторы с прямыми и инверсными выходами. Часть схемы на логических элементах И называется схемой выделения старшей единицы. Она выполняет функции дешифратора адреса в последующем в схеме ПЗУ на диодах. Выходной двоичный код считывается в выходной регистр.

Параллельные АЦП выпускаются разрядностью не более 8 и имеют быстродействие до 500 MSPS. Они находят применение при передаче видеоинформации и в системах регистрации очень быстрых процессов.

Параллельные АЦП большой разрядности имеют большую стоимость. Если необходимы АЦП с быстродействием 30 – 50 MSPS, то обычно применяют последовательно-параллельные АЦП, построенные на основе совокупности параллельных АЦП с малым количеством разрядов.

Дата добавления: 2015-09-05; просмотров: 67 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Структура АЦП последовательных приближений. | | | Тема 12. Принципы передачи изображений |