|

Читайте также: |

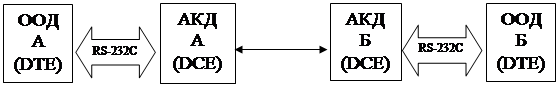

Интерфейс RS-232С предназначен для подключения аппаратуры, передающей или принимающей данные (АПД или ООД – оконечное оборудование данных), к оконечной аппаратуре каналов данных (АКД). В роли АПД может выступать компьютер, принтер, плоттер и другое периферийное оборудование. Этой аппаратуре соответствует аббревиатура DTE – Data Terminal Equipment. В роли АКД обычно выступает модем, этой аппаратуре соответствует аббревиатура DCE – Data Communication Equipment. Конечная цель подключения – соединение двух устройств DTE, полная схема соединений приведена на рисунке 3.

|

Линия

Рис.3 Полная схема соединения по RS-232С

Интерфейс позволяет исключить канал удалённой связи вместе с парой устройств DCE (модемов), соединения устройства DTE с помощью нуль-модемного кабеля (рисунок 4).

RS – 232С

RS – 232С

нуль-модем

Рис.4 Соединение двух устройств нуль-модемным кабелем

Стандарт реализует электрическую, информационную и конструктивную совместимости.

Особенность электрической совместимости – стандарт RS-232 С использует несимметричные передатчики и приёмники – сигнал передаётся относительно общего провода – схемной земли; интерфейс не обеспечивает гальванической развязки устройств. Логической единице соответствует уровень напряжения на входе приёмника в диапазоне –12...-3В. Для линий управляющих сигналов это состояние называется ON («включено»), для линий последовательных данных называется MARK. Логическому нулю соответствует напряжение в диапазоне +3...+12В. Для линий управляющих сигналов это состояние называется OFF («выключено»), для линий последовательных данных называется SPACE. Зона между уровнями –3...+3В – это зона нечувствительности, обусловливающая гистерезис приёмника. Уровни сигналов на выходах передатчиков –12...-5В и +5...+12В. Интерфейс предполагает наличие защитного заземления для соединяемых устройств, если они оба питаются от сети переменного тока и имеют сетевые фильтры.

Подключение и отключение интерфейсных кабелей устройств с автономным питанием (например, мышь) должно производиться при отключении питания.

Для интерфейса RS-232С специально выпускаются буферные микросхемы приёмников и передатчиков двуполярного сигнала.

Конструктивная совместимость реализуется регламентируемым типом разъёмов: на аппаратуре DTE (в том числе и на СОМ-портах РС) принято устанавливать вилки DB25-Р или более компактный вариант – DB9-Р.

Девятиштырьковые разъёмы не имеют контактов для дополнительных сигналов, реализующих синхронный режим.

На аппаратуре DCE (модемах) устанавливают розетки DB25-S или DB9-S. Разъёмы DCE могут непосредственно подключаться к разъёмам DTE или через «прямые» переходные кабели с розеткой и вилкой. Существуют переходники с 9 на 25-штырьковые разъёмы.

DB9S DB9Р

DB9S DB9Р

DB25S DB25Р

TD TD

| TD | |||||||

RD RD

| RD | |||||||

DTR DTR

| DTR | |||||||

DSR DSR

| DSR | |||||||

RTS RTS

| RTS | |||||||

CTS CTS

| CTS | |||||||

DCD DCD

| DCD | |||||||

RI RI

| RI | |||||||

SG SG

| SG |

Рис. 5 Кабели подключения модемов

Информационная совместимость реализуется назначением контактов разъёмов, управлением потоком передачи и скоростью обмена. В таблице 1 приведено назначение контактов разъёмов СОМ-портов (и любой другой аппаратуры DTE). Назначение контактов разъёмов DB25S определено стандартом EIA/TIA-232Е, разъём DB9S определён стандартом EIA/TIA-S74. У модемов (DCE) название цепей и назначение контактов, естественно, совпадает, но роли сигналов (вход-выход) меняются на противоположные.

Таблица 1. Разъёмы и сигналы интерфейса RS-232С

| Обозначение цепи | Контакт разъёма | Провод шлейфа выносного разъёма РС | Направление | |||||

| RS-232C | Стык2 | DB25S | DB9S | 1* | 2* | 3* | 4* | I/O |

| PG TD RD RTS CTS DSR SG DCD DTR RI | 108/2 | - | (10) | (10) | (10) | - O I O I I - I O I |

1* - шлейф 8-битных мультикарт;

2* - шлейф 16-битных мультикарт;

3* - вариант шлейфа портов на системных платах

4* - широкий шлейф к 25-контактному разъёму.

Подмножество сигналов RS-232С, относящихся к асинхронному режиму с точки зрения СОМ-порта РС приведены в таблице 2.

Таблица 2. Назначение сигналов интерфейса RS-232С

| Сигнал | Назначение |

| PG (Protect Ground) | Защитная земля, соединяется с корпусом устройства и экраном кабеля |

| SG (Signal Ground) | Сигнальная (схемная) земля, относительно которой действуют уровни сигналов |

| TD (Transmit Data) | Последовательные данные – выход передатчика |

| RD (Receive Data) | Последовательные данные – вход приёмника |

| RTS (Request To Send) | Выход запроса передачи данных: состояние «включено» уведомляет модем о наличии у терминала данных для передачи. В полудуплексном режиме используется для управления направлением – состояние «включено» |

| CTS (Clear To Send) | Вход разрешения терминалу передавать данные. Состояние «выключено» аппаратно запрещает передачу данных. Сигнал используется для аппаратного управления потоками данных. |

| DTR (Data Terminal Ready) | Выход сигнала готовности терминала к обмену данными. Состояние «включено» поддерживает коммутируемый канал в состоянии соединения. |

| DSR | Вход сигнала готовности от аппаратуры передачи данных (модем в рабочем режиме подключён к каналу и закончил действия по согласованию с аппаратурой на противоположном конце канала) |

| DCD (Data Carrier Detected) | Вход сигнала обнаружения несущей удалённого модема |

| RI (Ring Indicator) | Вход индикатора вызова (звонка). В коммутируемом канале этим сигналом модем сигнализирует о принятии вызова |

Для управления потоком данных могут использоваться два варианта протокола – аппаратный и программный.

Аппаратный протокол управления потоком RTS/CTS использует сигнал CTS, который позволяет остановить передачу данных, если приёмник не готов к их приёму. Работу этого протокола иллюстрирует рисунок 6.

Формат данных

Формат данных

| |||

| |||

TD ò ò

ò ò

ò ò

CTS

CTS

неготовность

неготовность

приёмника ò ò

приёмника ò ò

Рис.6 Аппаратное управление потоком

Программный протокол управления потоком XON/XOFF предполагает наличие двунаправленного канала передачи данных. Если устройство, принимающее данные, не может их принимать, оно по обратному каналу посылает байт-символ XOFF (13h). Противоположное устройство, приняв этот символ, приостанавливает передачу. Далее, когда принимающее устройство снова становится готовым к приёму данных, оно посылает символ XON (11h), приняв который противоположное устройство возобновляет передачу.

TD

TD

ò ò

RD

RD

ò ò

XOFF XON

неготовность

неготовность

приёмника ò ò

программная реакция

передатчика на XON/XOFF

передатчика на XON/XOFF

Рис.7 Программное управление потоком XON/XOFF

Для исключения потерь данных приёмник должен иметь буфер принимаемых данных.

Описанные стандартные протоколы поддерживаются как устройствами, так и операционными системами. Некоторые плоттеры используют программное управление, посылая не символы XON/XOFF, а слова (ASCII-строки). Такие плоттеры рассчитаны на прямой диалог с прикладной программой.

Аппаратная реализация СОМ-портов

СОМ-порты ХТ/АТ базируются на микросхемах UART (Universal Asynchronus Receiver Transmitter) – универсальный асинхронный приёмопередатчик (УАПП). Эти микросхемы осуществляют преобразование параллельного кода в последовательный при передаче данных и обратное преобразование при приёме данных. Они формируют и обрабатывают управляющие сигналы интерфейса RS-232С (управление и состояние модема).

СОМ-порты ХТ/АТ используют микросхемы, совместимые на уровне регистров с UART i8250-8250/16450/16550А.

В компьютерах класса АТ применяют микросхемы UART следующих модификаций:

- 16450 – быстродействующая версия 8250. Эта микросхема обеспечивает минимум, требуемый ОС/2 для работы с СОМ-портами;

- 16550 – развитие 16450. Может использовать канал DMA для обмена данными. Имеет FIFO-буфер, но некорректность его работы не позволяет им воспользоваться;

- 16550А – имеет работающие 16-байтные FIFO-буферы приёма и передачи и возможность использования DMA. Обеспечивает обмен на скоростях 9600 бит/с и выше без потери данных. Большинство универсальных микросхем контроллеров портов ввода/вывода, входящих в чипсеты современных системных плат обеспечивают совместимость с этой микросхемой.

С программной точки зрения UART 16550А представляет набор регистров, доступ к которым определяется адресом (смещением адреса регистра относительно базового адреса порта) и значением бита DLAB (бита 7 регистра LCR – регистр управления линией – настройки параметров канала). В адресном пространстве микросхема занимает 8 смежных адресов. Список регистров и способы доступа к ним приведены в таблице 3.

Таблица 3. Регистры UART 16550А

| Доступ | Регистр | Чтение/запись R/W | ||

| смещение | DLAB | имя | название, назначение | |

| 0h | THR | Transmit Holding Register – промежуточный регистр данных передатчика | WO | |

| 0h | RBR | Receiver Buffer Register –буферный регистр принимаемых данных | RO | |

| 0h | DLL | Divisor Latch LSB – регистр младшего байта делителя частоты | R/W | |

| 1h | DLM | Divisor Latch MSB – регистр старшего байта делителя частоты | R/W | |

| 1h | IER | Interrupt Enable Register – регистр разрешения прерывания | R/W | |

| 2h | X | IIR | Interrupt Identification Register – регистр идентификации прерываний и признака режима FIFO | RO |

| 2h | X | FCR | FIFO Control Register – регистр управления FIFO | WO |

| 3h | X | LCR | Line Control Register – регистр управления линией (настройка параметров канала) | R/W |

| 4h | X | MCR | Modem Control Register – регистр управления модемом | R/W |

| 5h | X | LSR | Line Status Register – регистр состояния линии | R/W* |

| 6h | X | MSR | Modem Status Register – регистр состояния модема | R/W* |

| 7h | X | SCR | Scratch Pad Register – рабочий регистр (8 бит) | R/W |

* Некоторые биты допускают только чтение. Запись в регистр может привести к сбою протокола.

Рассмотрим использование регистров UART 16550А.

THR – данные, записанные в этот регистр будут пересланы в выходной сдвигающий регистр (когда он будет свободен), из которого поступят на выход при наличии разрешающего сигнала CTS. Бит 0 передаётся и принимается первым. Если длина посылки менее 8 бит, старшие биты равны нулю (игнорируются).

RBR – заносятся данные, принятые входным сдвигающим регистром для последующего считывания процессором.

DLL, DLM – регистры делителя частоты. Делитель определяет по формуле D=115200/V, где V – скорость передачи, бит/с. Входная частота синхронизации 1,8432 МГц делится на заданный коэффициент, после чего получается 16-кратная частота передачи данных.

IER – регистр разрешения прерывания. Единичное значение бита разрешает прерывание от соответствующего источника:

биты 7-4 = 0 – не используются

бит 3 – по изменению состояния модема (любой из линий CTS, DSR, RI, DCD) – ModIE

бит 2 – по обрыву/ошибке линии - RхLIE

бит 1 – по завершению передачи - ТхDE

бит 0 – по приёму символа (в режиме FIFO – прерывание по тайм-ауту) – RxDIE

IIR – регистр идентификации (только для чтения) прерываний и признака режима FIFO. Для упрощения программного анализа UART выстраивает внутренние запросы прерывания по 4-х уровневой приоритетной системе. Порядок приоритетов (по убыванию): состояние линии, приём символа, освобождение регистра передатчика и состояние модема. При возникновении условий прерывания UART указывает на источник с высшим приоритетом до тех пор, пока он не будет сброшен соответствующей операцией. Только после этого будет выставлен запрос с указанием следующего источника:

биты 7:6 – признак режима FIFO:

11 – режим FIFO 16550A;

10 – режим FIFO 165550;

00 – обычный режим.

биты 5:4 – не используются;

бит 3 – прерывания по тайм-ауту (не в режиме FIFO);

биты 2:1 – причина прерывания с наивысшим приоритетом (не в режиме FIFO):

11 – ошибка/обрыв линии; сброс - чтением регистра состояния лини;

10 – принят символ; сброс – чтением данных;

01 – передан символ (регистр THR пуст); сброс – записью данных;

00 – изменение состояния модема; сброс – чтением регистра состояния модема.

бит 0 – признак необслуженного запроса прерывания:

1 – нет запроса 0 – есть запрос

В режиме FIFO причину прерывания идентифицируют биты (3:1):

011 – ошибка/обрыв линии; сброс – чтением регистра состояния линии;

010 - принят символ; сброс – чтением регистра данных приёмника;

110 – индикатор тайм-аута (за 4-х кратный интервал времени передачи символа не передано и не принято ни одного символа, хотя в буфере имеется, по крайней мере, один). Сброс – чтением регистра данных приёмника;

001 – регистр THR пуст; сброс – записью данных;

000 – изменение состояния модема (CTS, DSR, RI или DCD); сброс – чтением регистра MSR;

FCR – регистр управления FIFO (только для записи). Назначение бит:

биты 7:6 – ITL (Interrupt Trigger Level) – уровень заполнения FIFO – буфера, при котором вырабатывается прерывание:

00 – 1 байт;

01 – 4 байта;

10 – 8 байт;

11 – 14 байт;

биты 5:4 – зарезервированы;

бит 3 – разрешение операций DMA;

бит 2 сброс счётчика FIFO – передатчика (запись 1 – сбрасывает) сдвигающий регистр не сбрасывается;

бит 1 – то же, что и бит 2 для приёмника;

бит 0 – разрешение (1) режима FIFO для передатчика и приёмника;

LCR – регистр управления линией (настройка параметров канала):

бит 7 – DLAB (Divisor Latch Access Bit) – управление доступом к делителю частоты

бит 6 – формирование обрыва линии (посылка нулей при бит 6=1)

бит 5 – принудительное формирование бита паритета

0 – контрольный бит генерируется в соответствии с паритетом выводимого символа

1 – постоянное значение контрольного бита при чётности – нулевое, нечётности – единичное

бит 4 – выбор типа контроля

0 – нечётность, 1 – чётность

бит 3 – разрешение контрольного бита

1 – разрешение, 0 – запрещён

бит 2 – количество стоп-бит

0 – 1 стоп-бит, 1 – 2 стоп-бита

биты 1:0 – количество бит данных

00 – 5 бит, 01 – 6 бит,

10 – 7 бит, 11 – 8 бит

MCR – регистр управления модемом:

биты 7:5 – зарезервированы;

бит 4 – разрешение режима диагностики:

0 – нормальный режим;

1 – режим диагностики;

бит 3 – разрешение прерываний (с помощью внешнего входа OUT2):

0 – запрещены, 1 – разрешены

В диагностическом режиме поступает на вход MSR.7;

бит 2 – управление выходным сигналом 1 (не используется)

В диагностическом режиме поступает на вход MSR.6;

бит 1 – управление выходом RTS:

1 – активен (-V), 0 – пассивен (+V)

В диагностическом режиме поступает на вход MSR.5

LSR – регистр состояния приёмопередатчика:

бит 7 – ошибка принятых данных в режиме FIFO (буфер содержит хоть один символ принятый с ошибкой формата, паритета или обрывом). В не FIFO режиме всегда 0;

бит 6 – регистр передатчика пуст (нет данных для передачи ни в сдвиговом регистре, ни в буферных, THR или FIFO);

бит 5 – регистр передатчика готов принять байт для передачи. В режиме FIFO указывает на отсутствие символов в FIFO – буфере передачи. Вызывает прерывание;

бит 4 – индикатор обрыва линии (вход приёмника находится в состоянии логического нуля не менее, чем время посылки символа);

бит 3 – ошибка кадра (неверный стоп-бит);

бит 2 – ошибка контрольного бита (паритета или фиксирования);

бит 1 – переполнение (потеря символа);

бит 0 – принятые данные готовы. Сброс – чтением приёмника.

Индикаторы ошибок – биты 4:1 – сбрасываются после чтения регистра LSR.

MSR – регистр состояния модема:

биты 7,6,5,4 – состояние линий DCD, RI, DSR, CTS соответственно;

биты 3,2,1,0 – изменение состояний линий DCD, RI, DSR, CTS соответственно. Признаки изменения сбрасываются по чтению регистра;

SCR – рабочий регистр (8 бит) предназначен для временного хранения данных. На работу UART влияния не оказывает.

В диагностическом режиме (при бите 4 = 1 регистра MCR) внутри UART организуется внутренняя «заглушка»:

- выход передатчика переводится в состояние логической единицы;

- вход приёмника отключается;

- выход сдвигающего регистра передатчика логически сдвигается со входом приёмника;

- входы DSR, CTS, RI и DCD отключаются от входных линий, на них внутренне подаются сигналы DTRC, RTSR, OUT1C, IE;

- выходы управления модемом переводятся в пассивное состояние (логический ноль).

При этом передаваемые данные в последовательном виде немедленно принимаются, что позволяет проверить внутренний канал данных порта (включая сдвигающие регистры) и отработку прерываний, а также определить скорость работы UART.

Дата добавления: 2015-08-27; просмотров: 96 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Последовательный интерфейс | | | Средства BIOS для работы с СОМ-портами |