|

Читайте также: |

Сумматоры - это цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах.

По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие – запоминающие результаты вычислений при снятии входных сигналов.

В дальнейшем будут рассматриваться только комбинационные сумматоры, на основе которых выполняется большинство суммирующих ИС.

Сумматор по модулю два - Это устройство с двумя входами (а и b), на выходе у которого сигнал "1" появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. "0" и "1". Сумматор не обладает памятью.

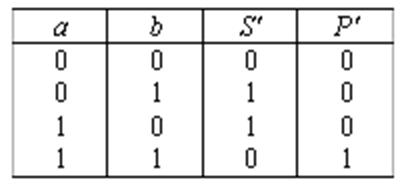

Eго таблица истинности и логическое уравнение имеют вид:

Название “по модулю два” этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 21)

Рис. 21. Реализация сумматора по модулю два:

а – принципиальная схема; б – функциональная схема

Полусумматор - Обеспечивает операцию сложения двух одноразрядных двоичных чисел a и b. Так как при a = 1 и b = 1 получается перенос единицы в следующий разряд, полусумматор должен иметь два выхода: с одного снимается сигнал суммы по модулю два, а с другого - сигнал переноса.

Таблица истинности полусумматора и его логические уравнения имеют вид:

P' = ab

Реализация полусумматора в базисе И–НЕ представлена на рис. 22

а б

Рис. 22. Схема полусумматора:

а – реализация в базисе И–НЕ; б – условное обозначение

Условное обозначение полусумматора на схемах – HS (halfsum – полусумма), а полного сумматора – SM.

Полный сумматор - Это устройство для сложения трех одноразрядных двоичных чисел a, b, c, где c - сигнал переноса из предыдущего младшего разряда. Имеет два выхода S (сумма) и Р (перенос).

Полный сумматор можно построить из двух полусумматоров (рис. 23), отсюда и название – полусумматор, используя следующие логические уравнения

Рис. 23. Полный сумматор

На основе полного сумматора можно построить суммирующие устройства параллельного или последовательного действия для сложения многоразрядных двоичных чисел.

В цифровой схемотехнике операцию вычитания обычно заменяют сложением уменьшаемого с вычитаемым, представленным в дополнительном коде, поэтому вычитатели могут быть выполнены на основе сумматоров.

Дата добавления: 2015-07-11; просмотров: 144 | Нарушение авторских прав

| <== предыдущая страница | | | следующая страница ==> |

| Быстродействие | | | Дешифраторы, шифраторы, преобразователи кодов |